verilog_base_study

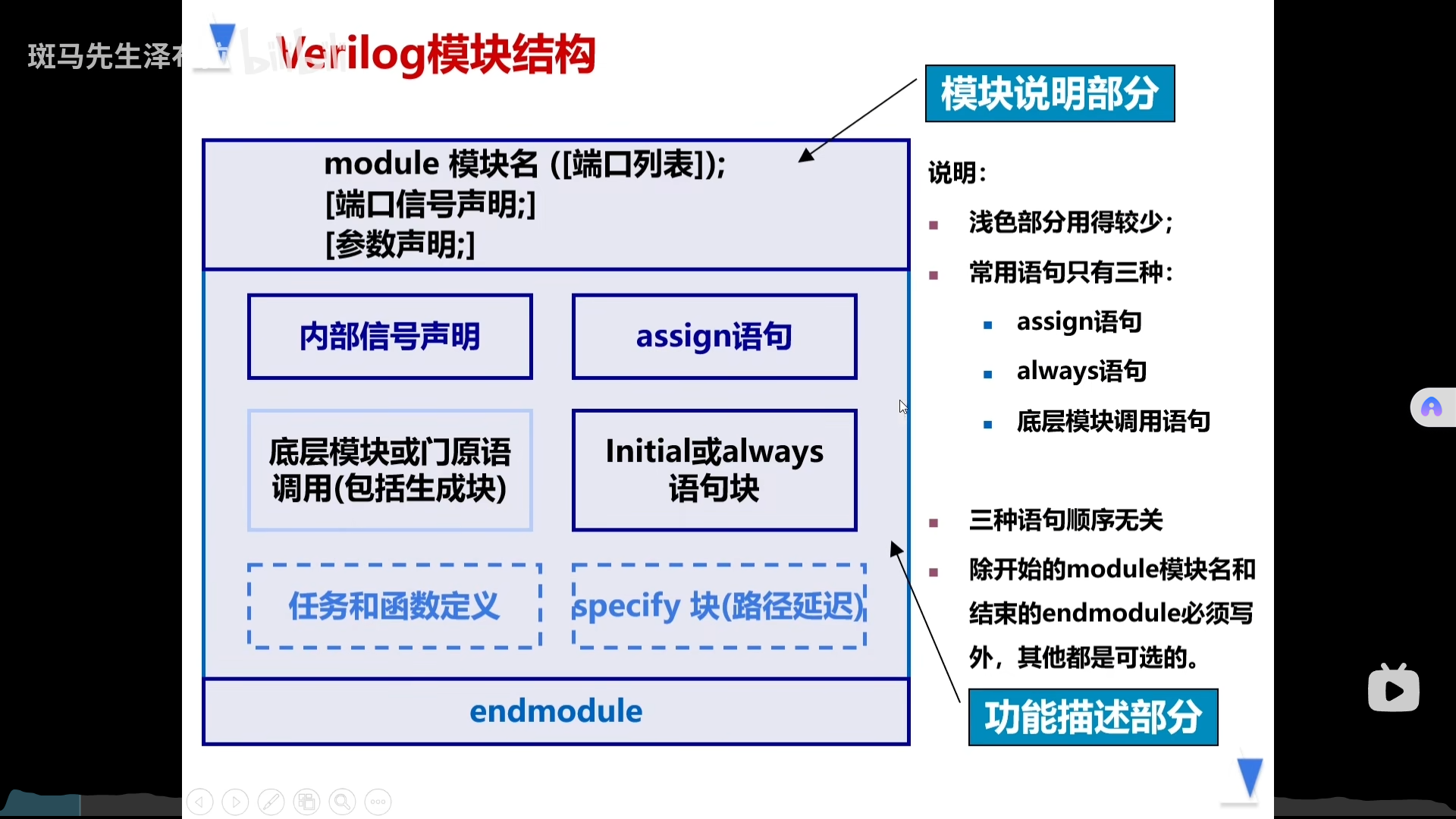

verilog 模块结构

verilog基本框架

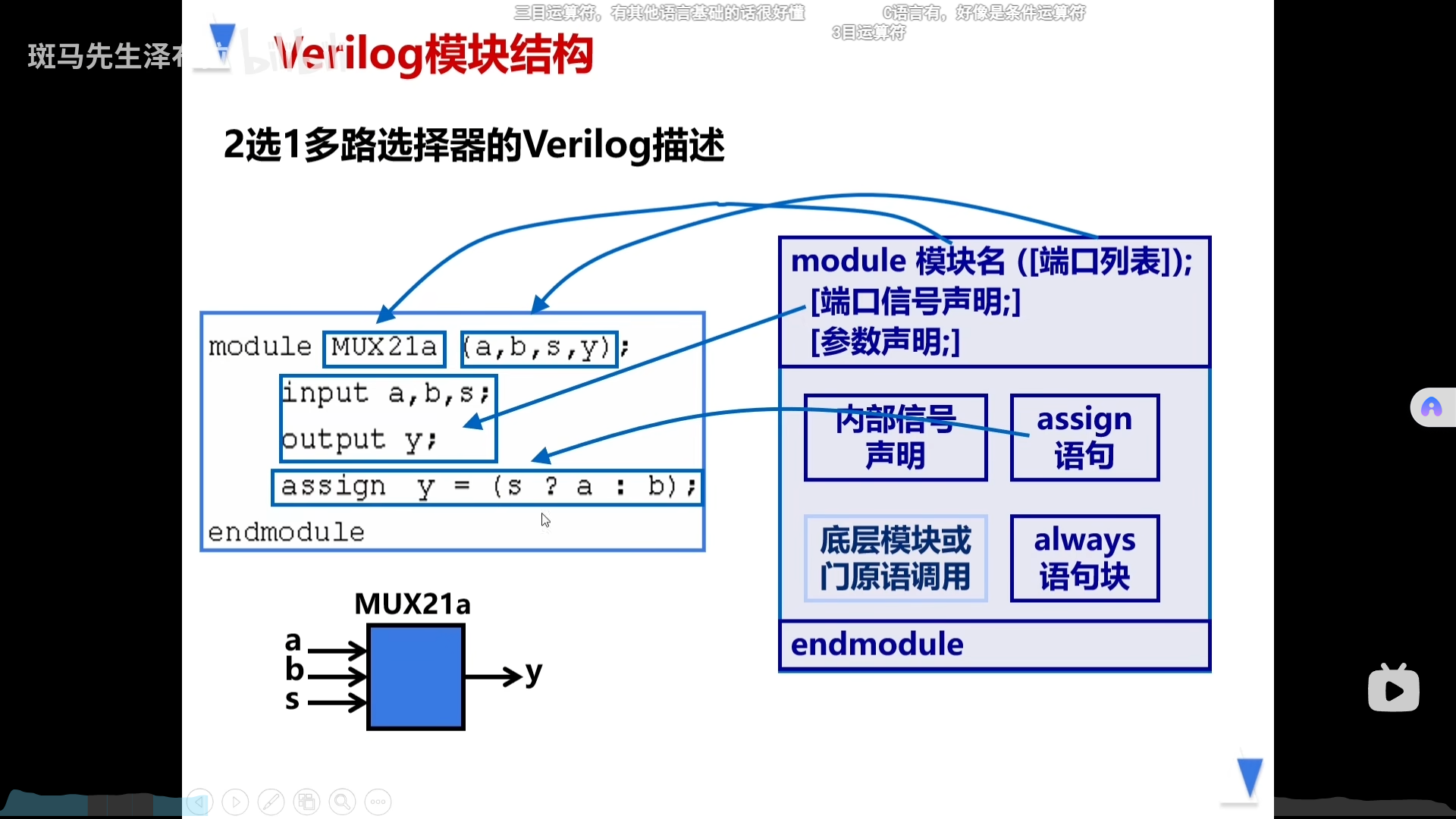

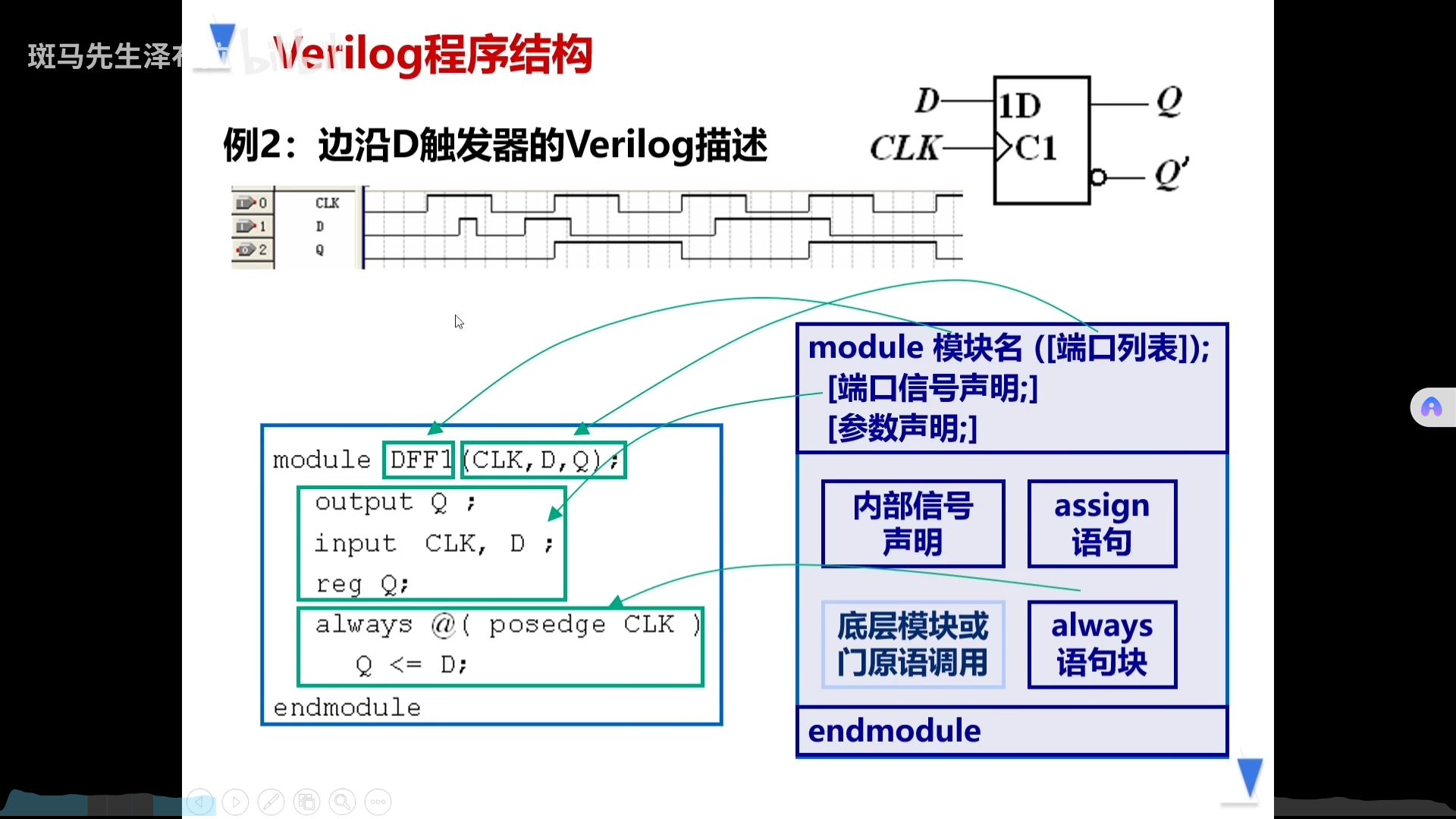

实例、

进行实例化对象,以二选一选择器和D触发器为例,涉及到always和assign

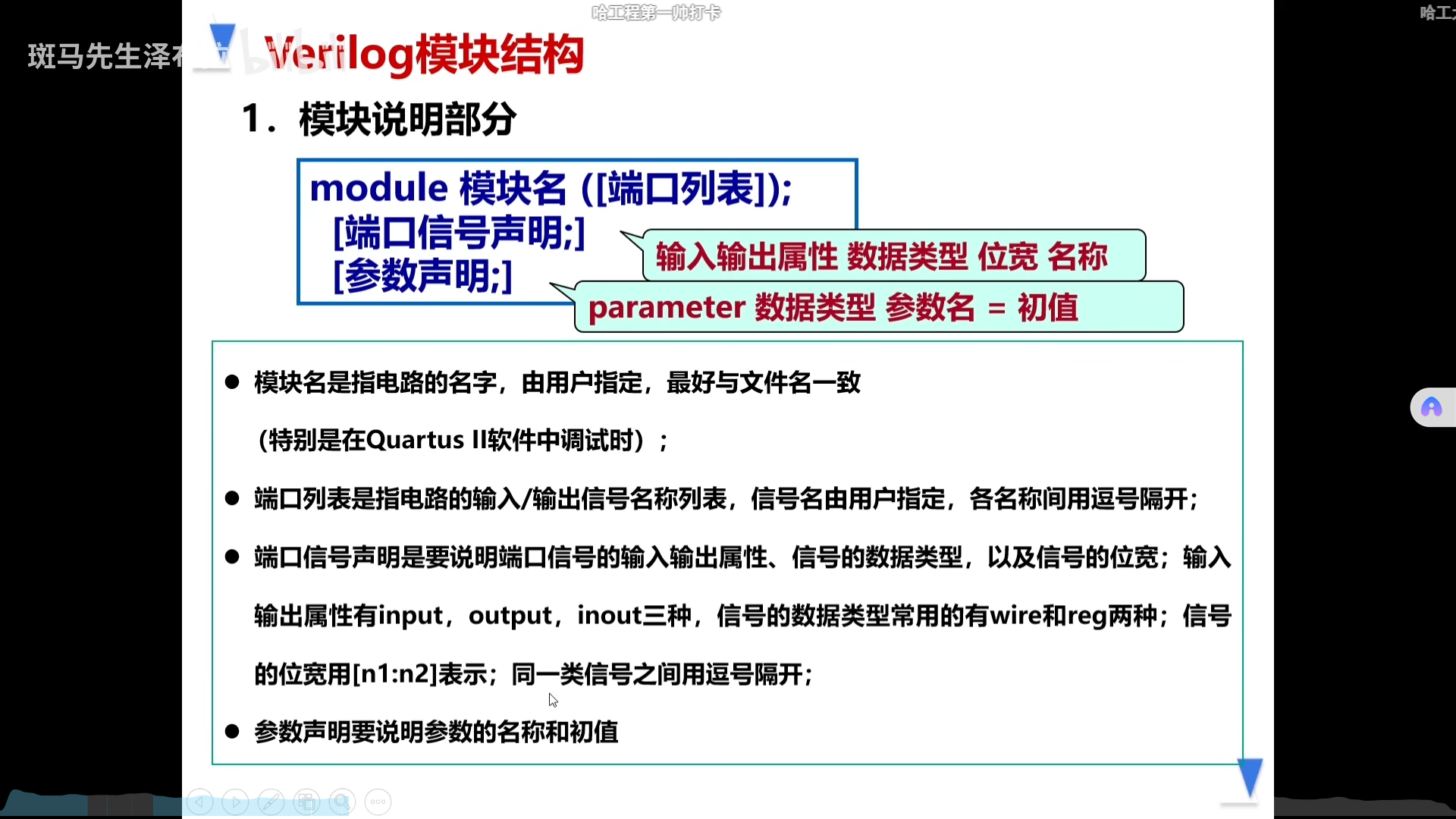

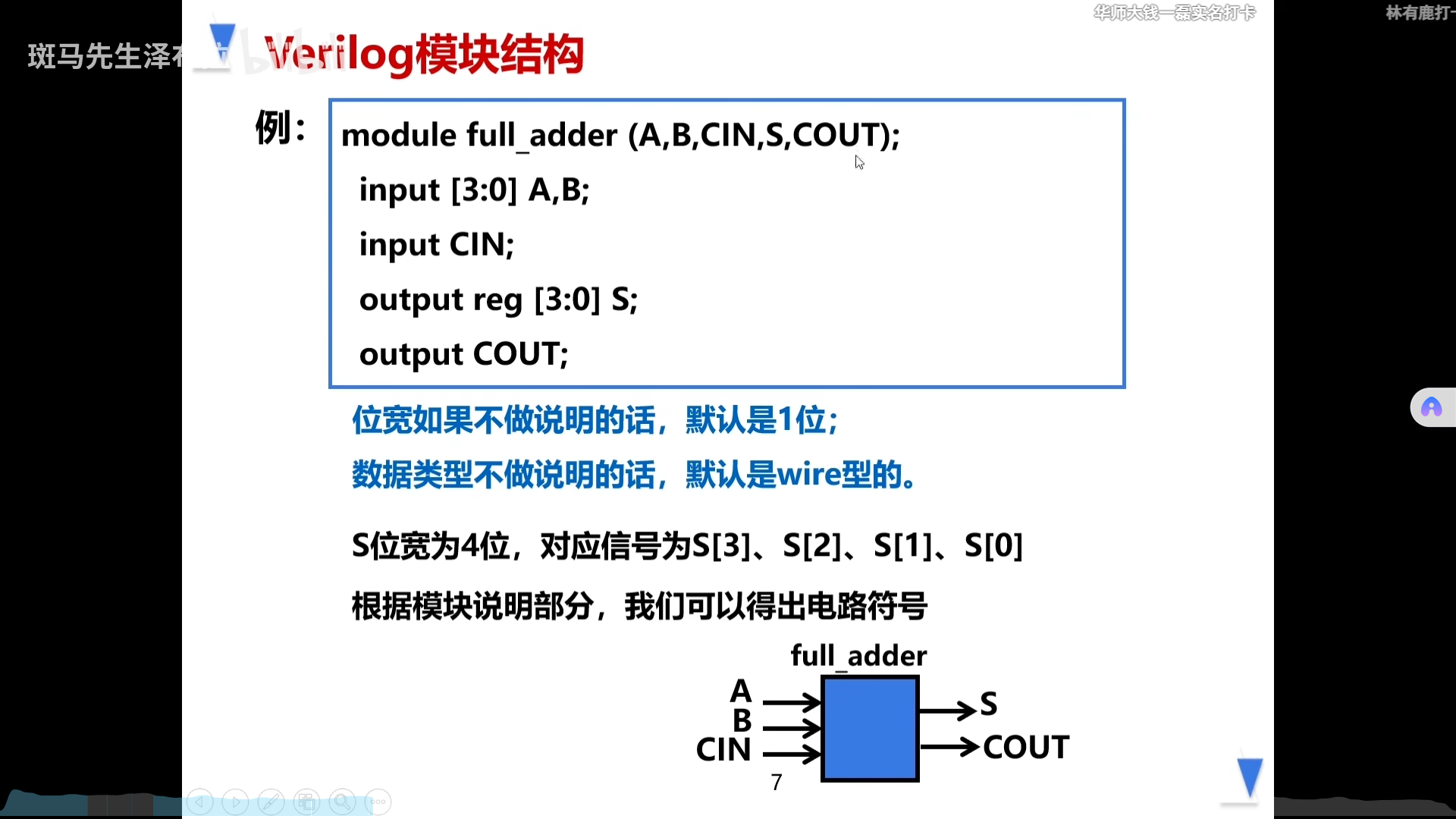

模块说明部分

模块说明部分的涉及及其注意事项

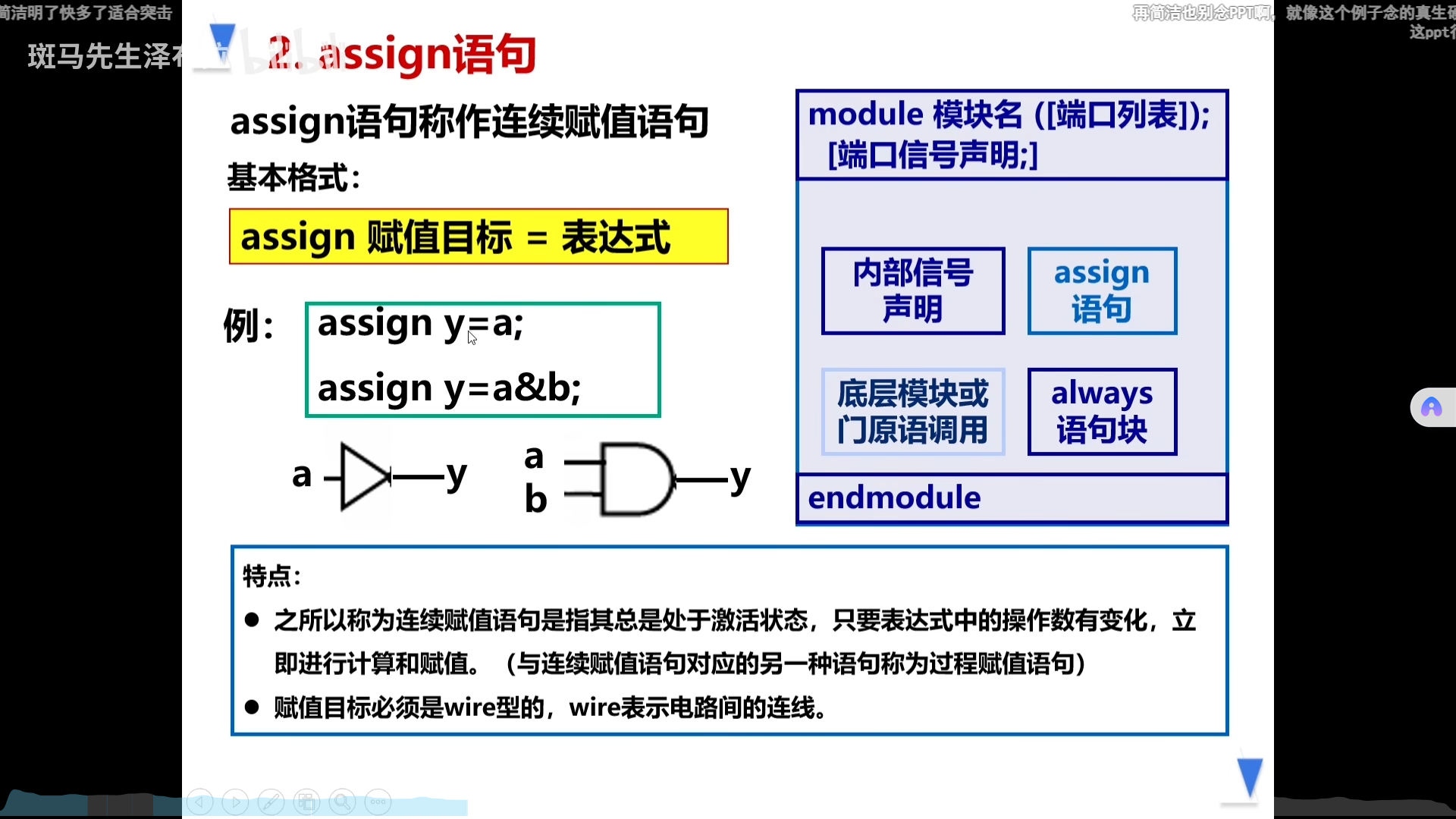

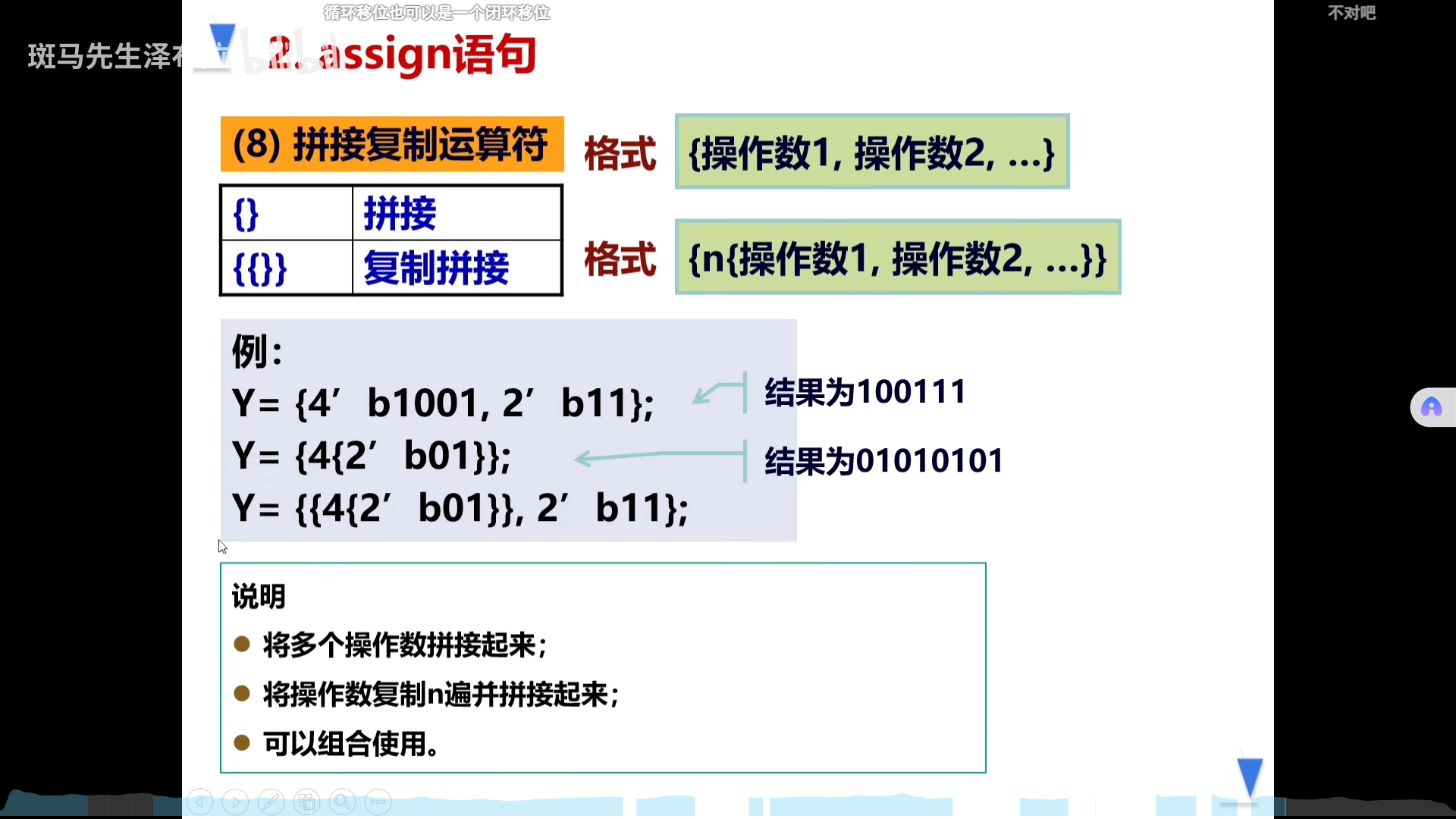

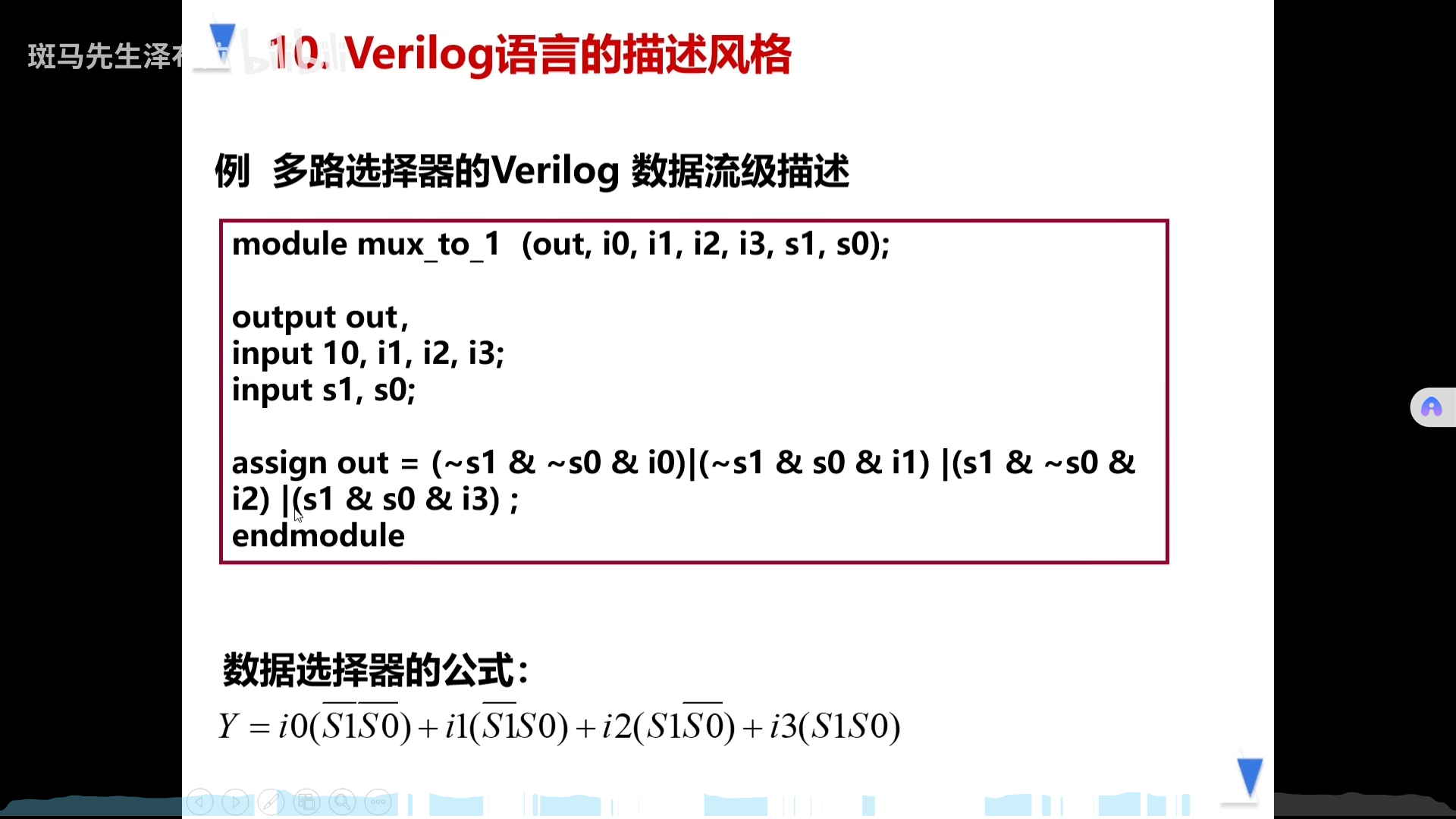

assign语句

进入assign语句,注意事项,必须=,且wire类型

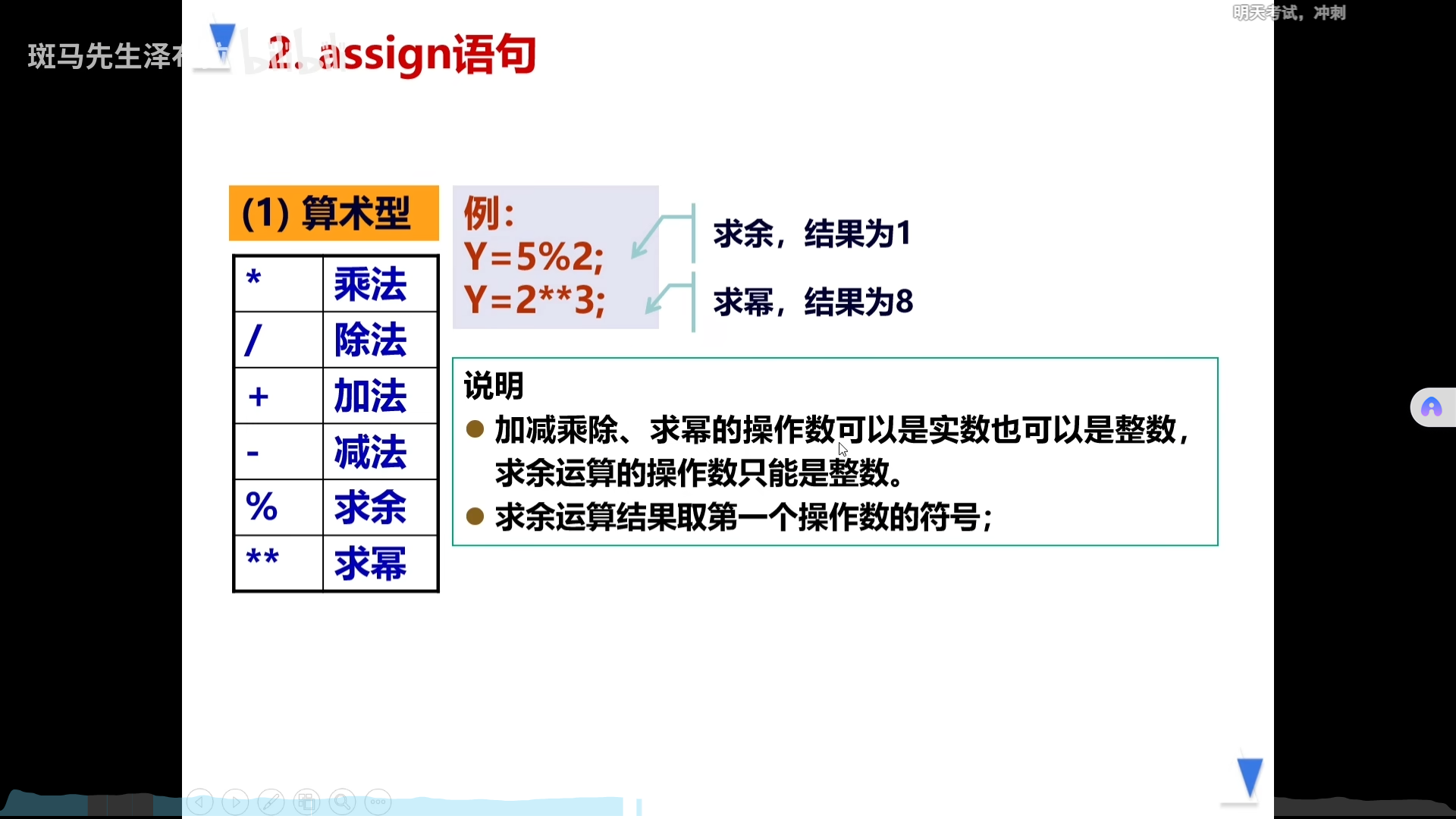

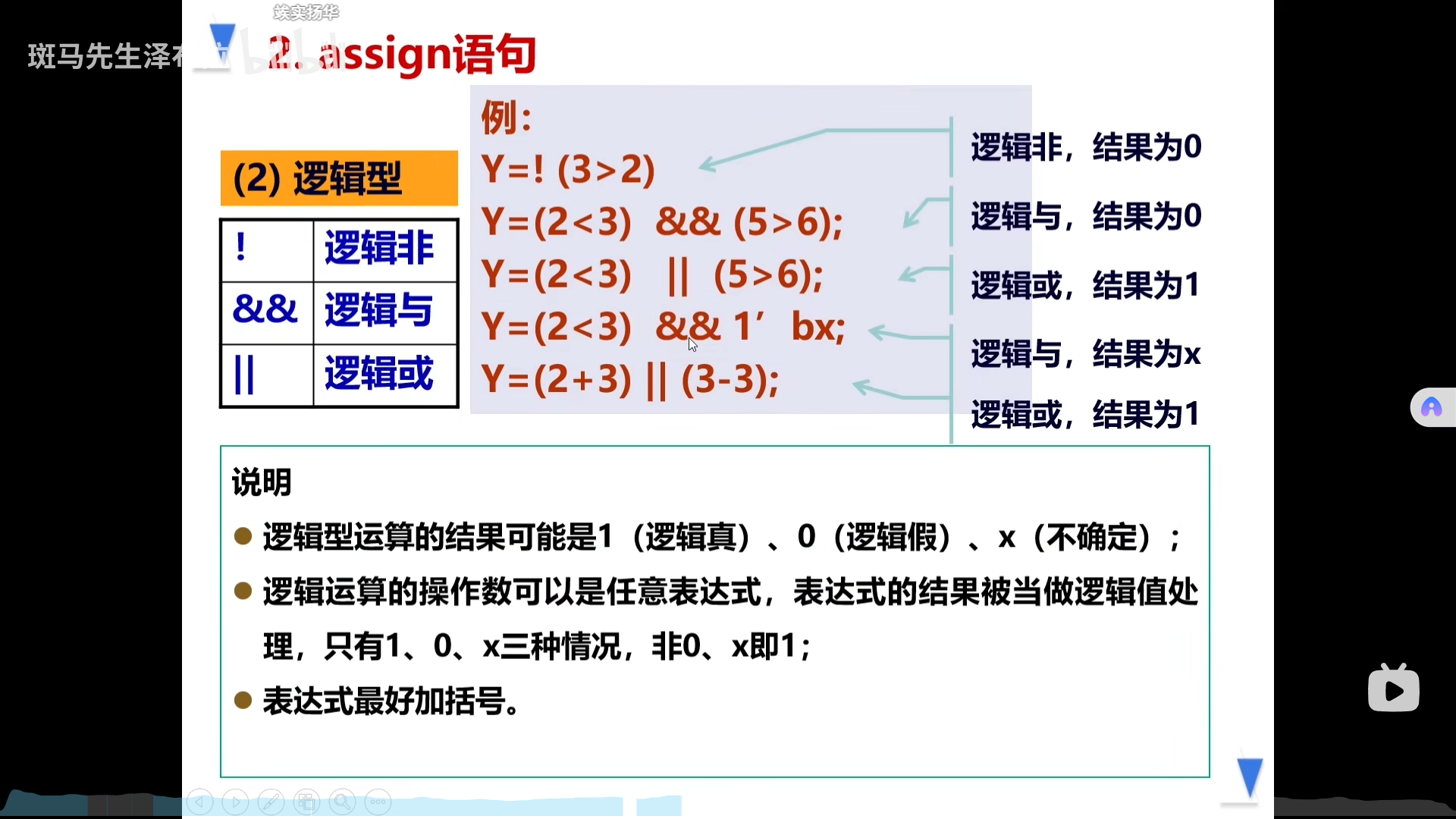

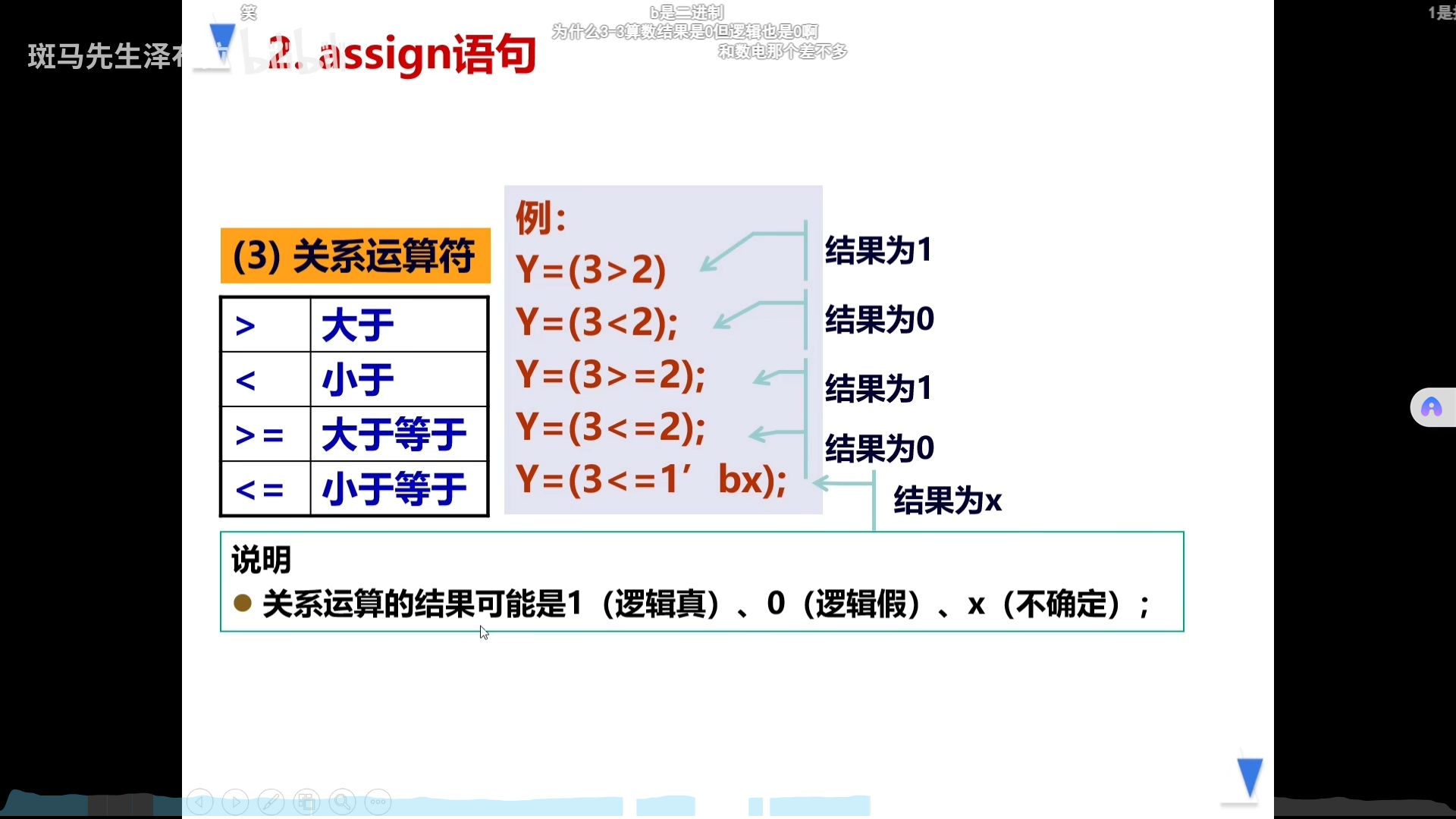

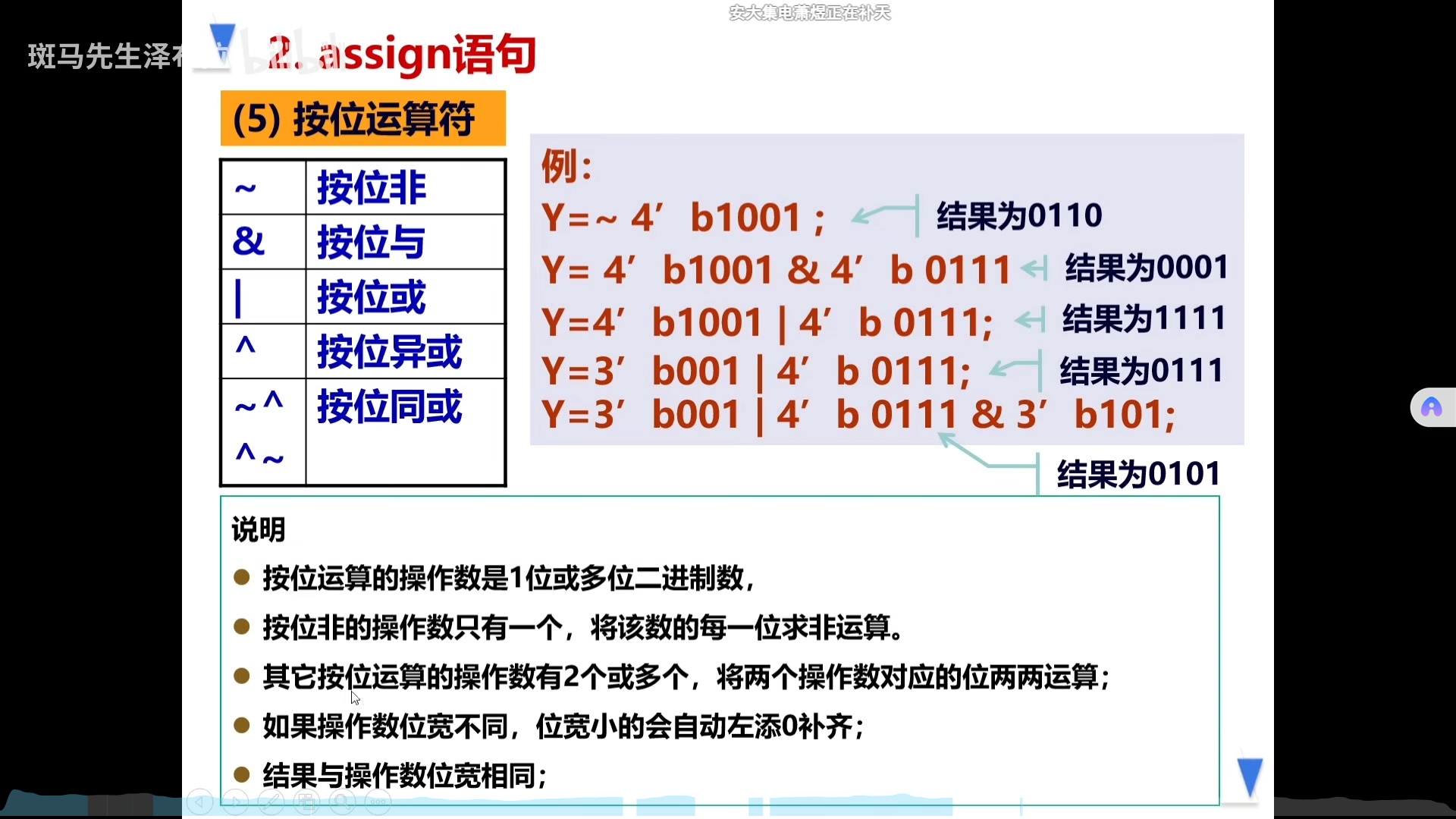

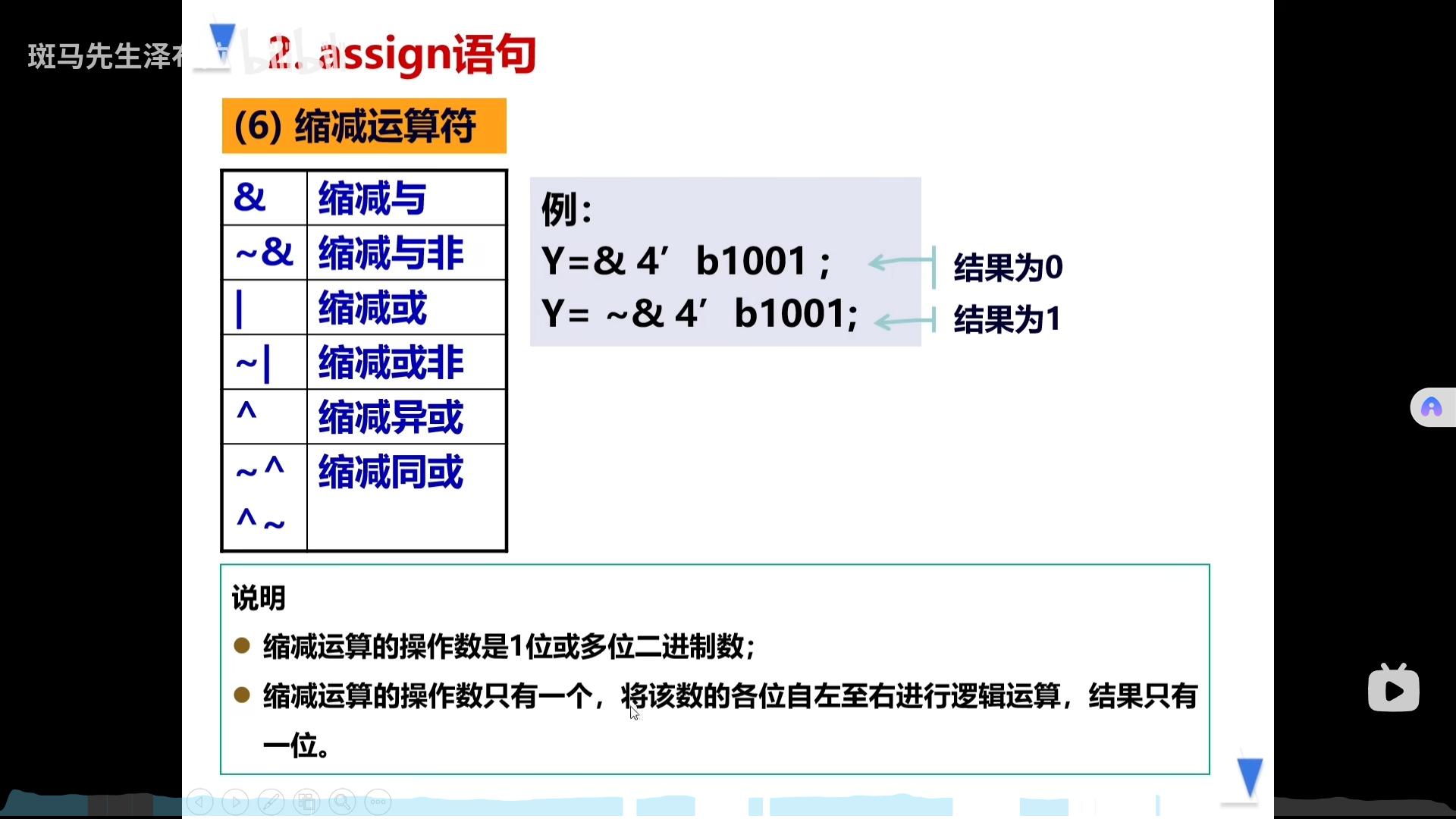

assign操作

基本运算符号及其类型

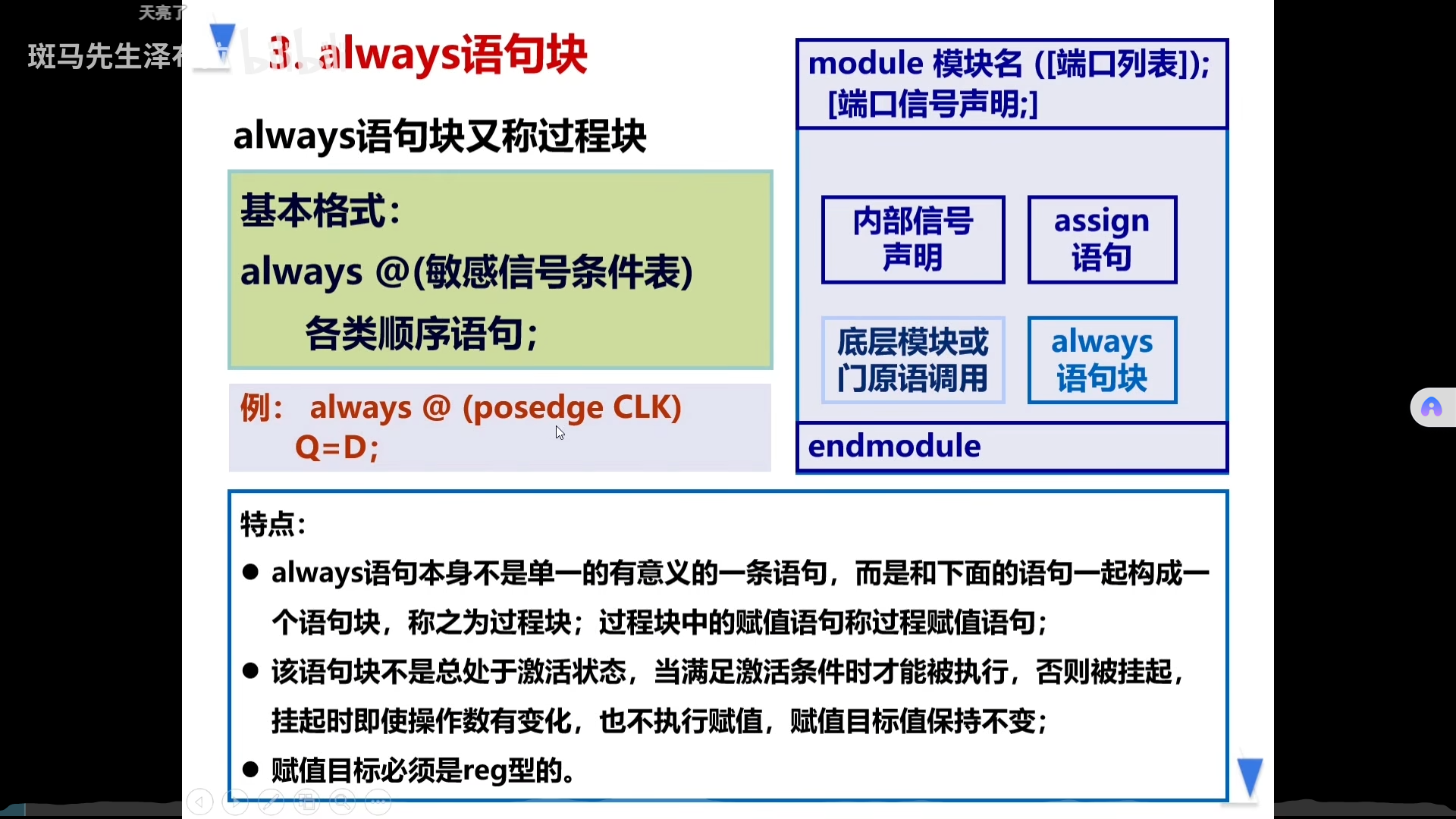

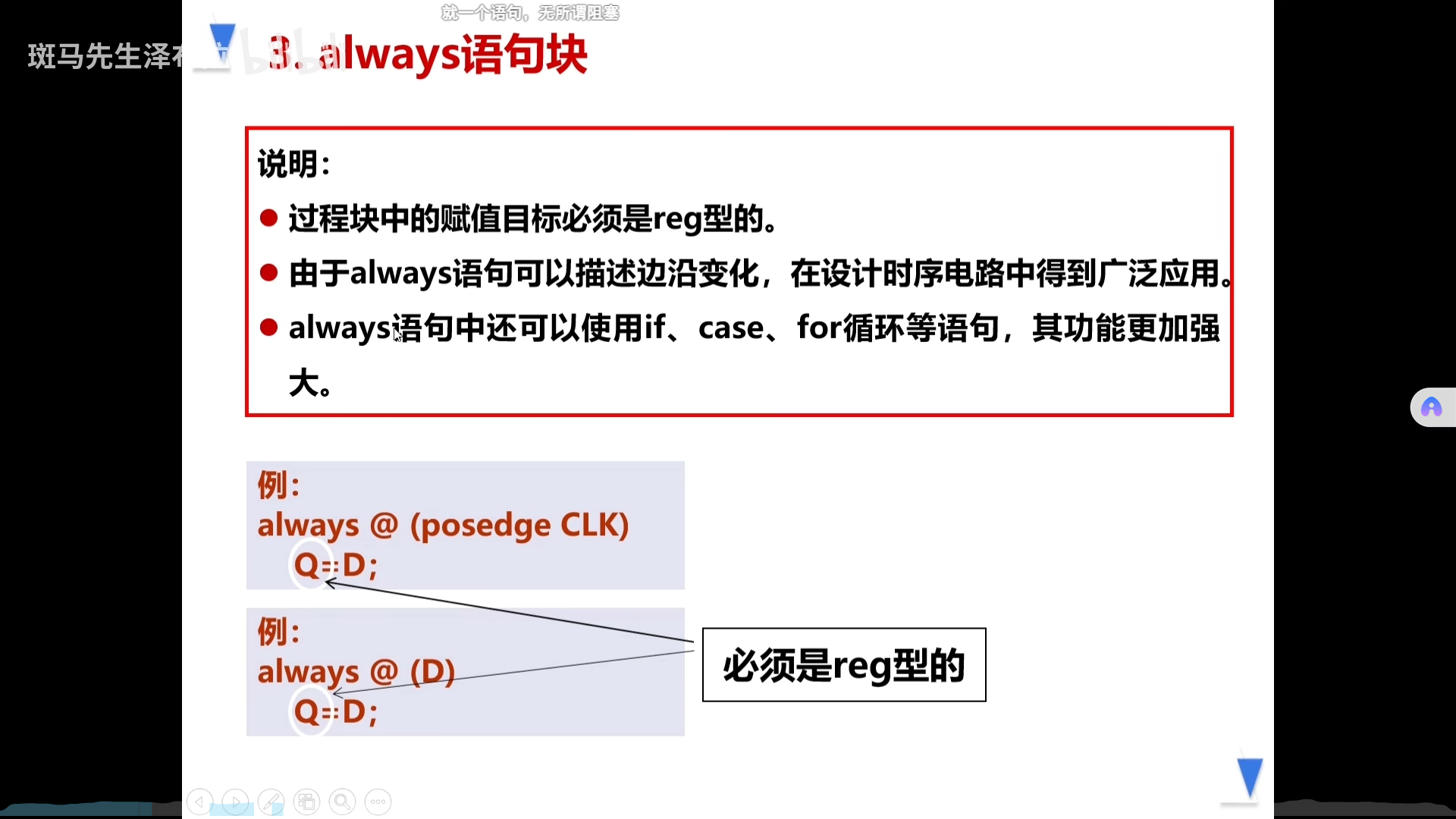

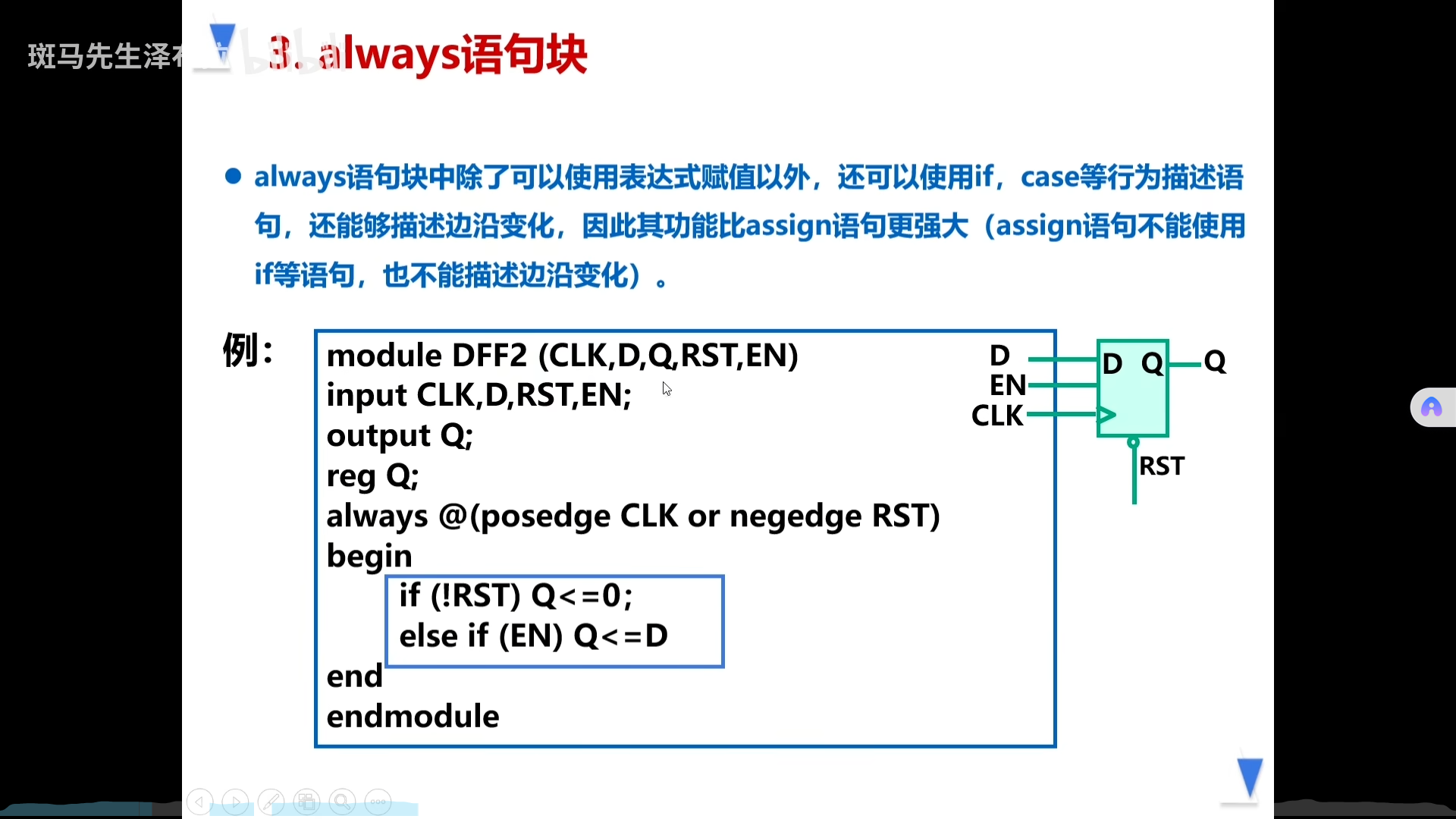

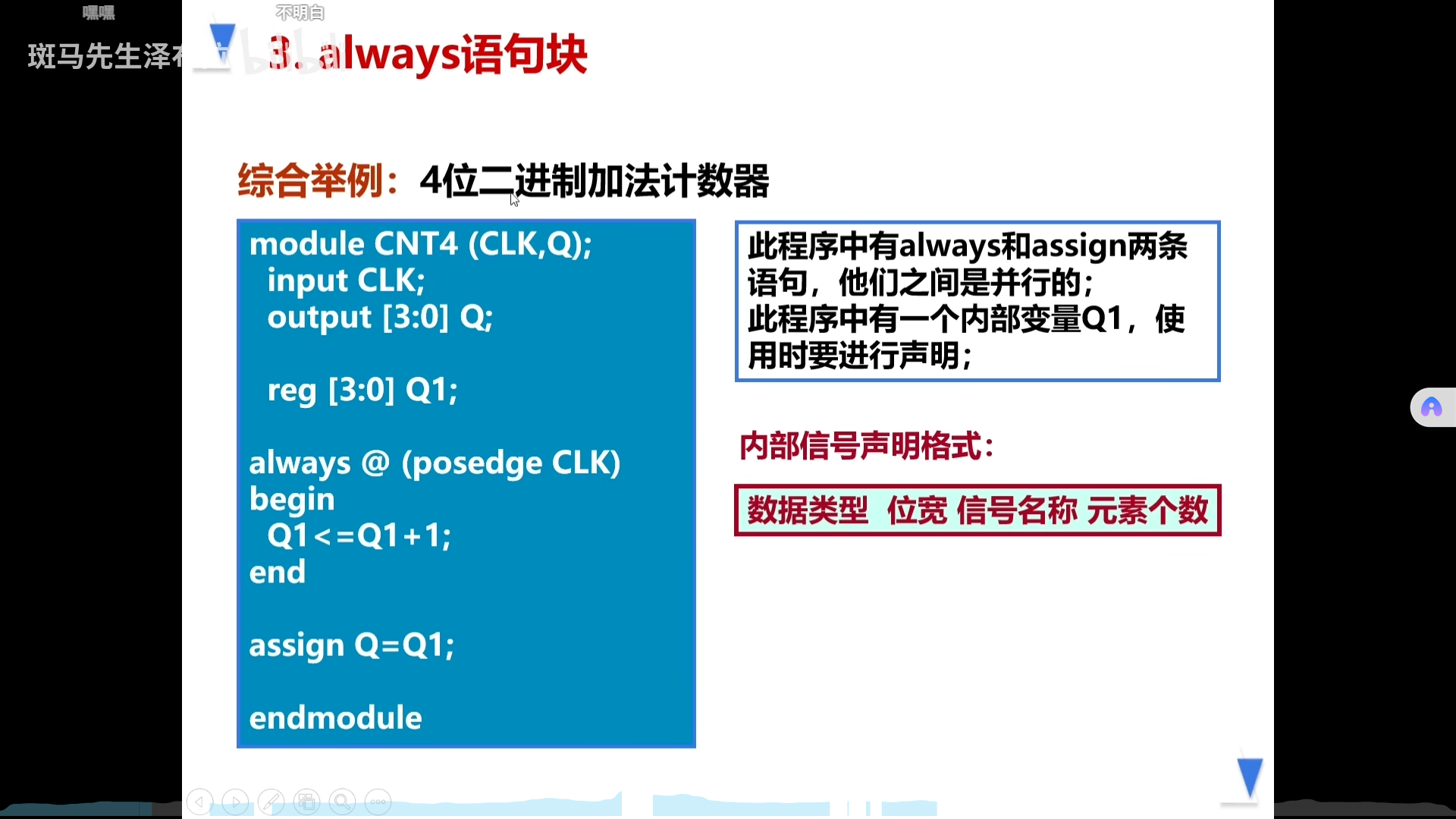

always语句

always表示总是如此,@表示等待,赋值目标必须为reg类型

目标条件有两种,边沿触发和电平触发

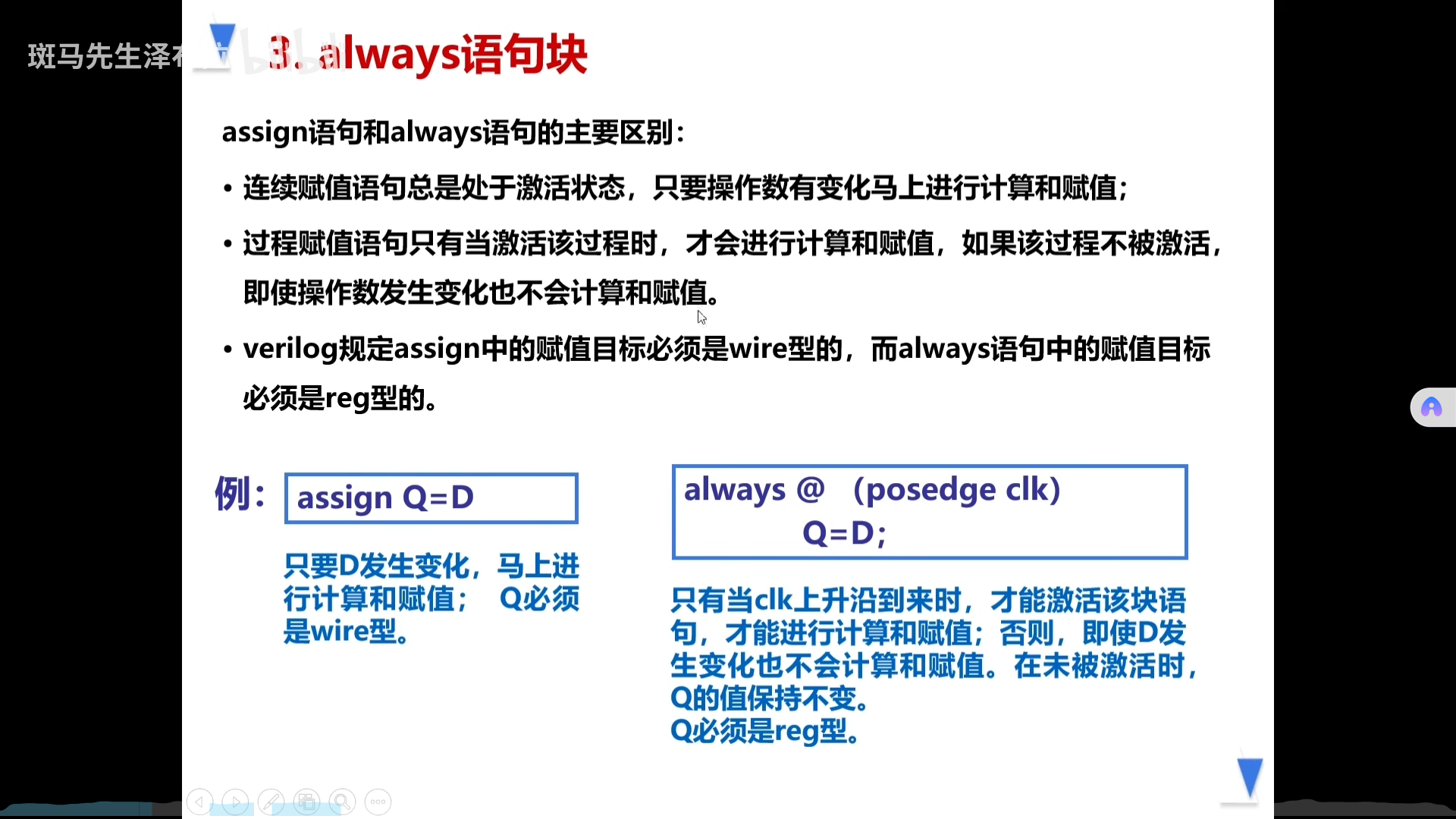

assign与always的区别

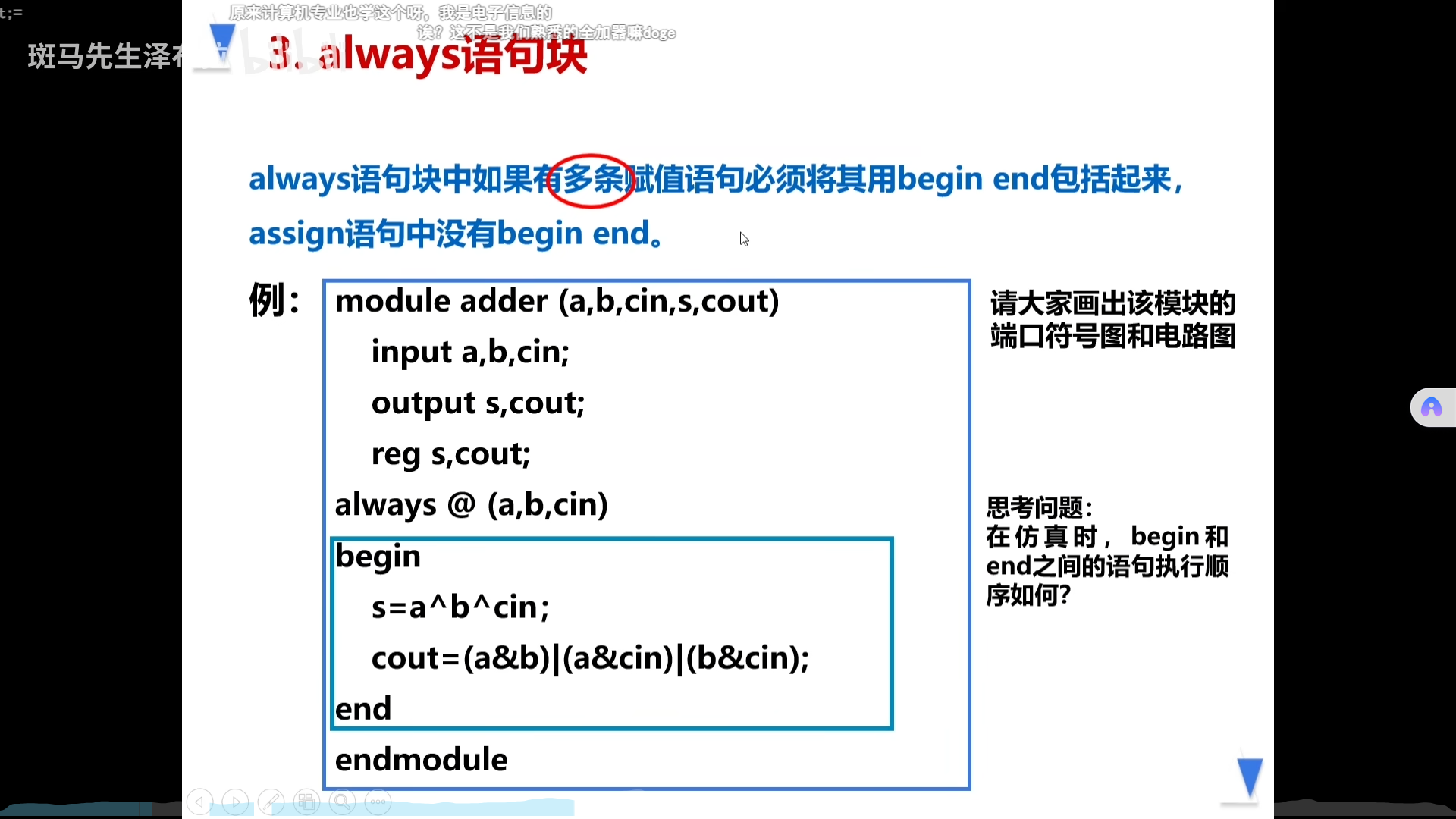

begib end 的使用

相当于括号,always如果有多条赋值语句,必须用begin end 将其包裹

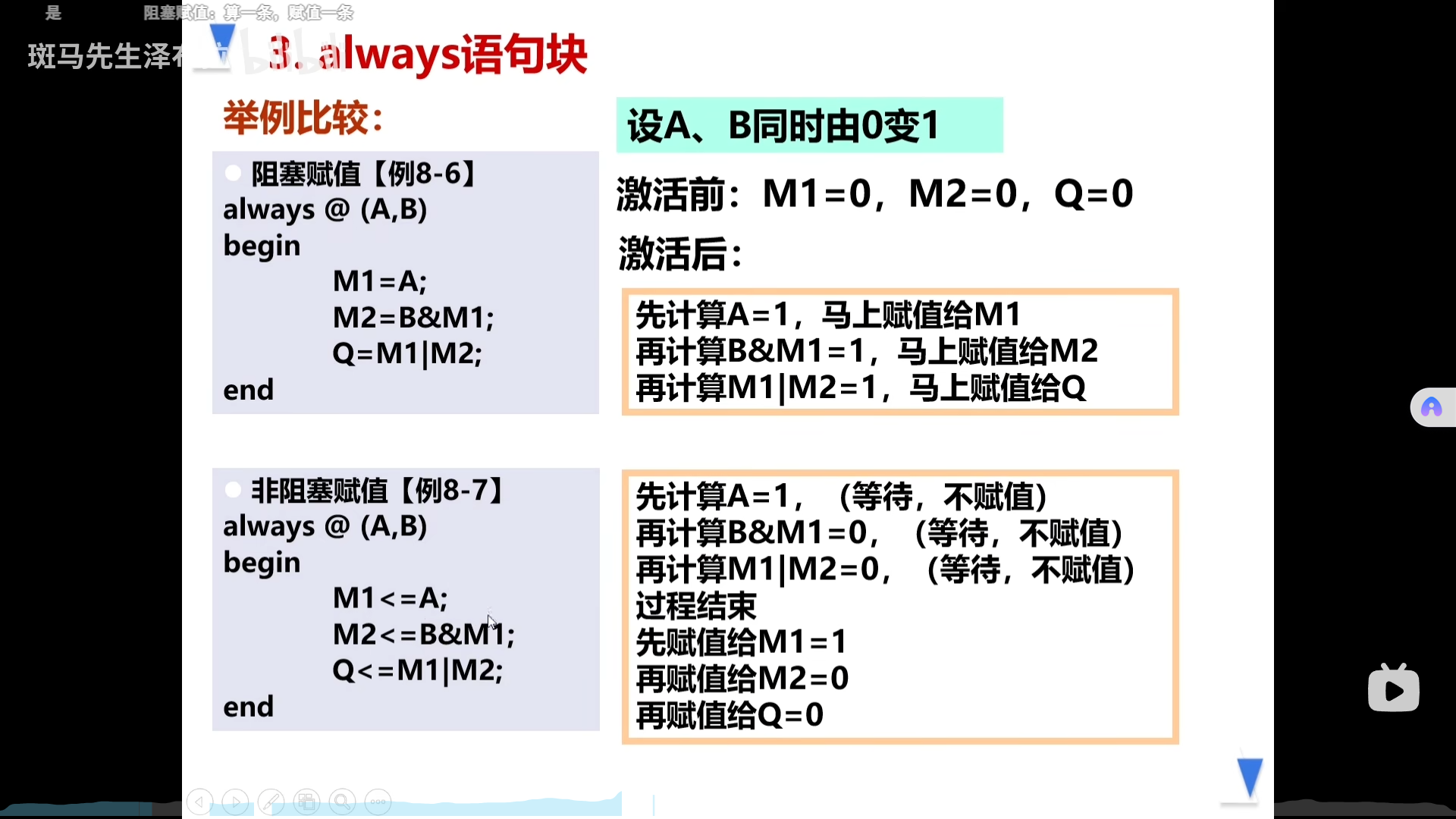

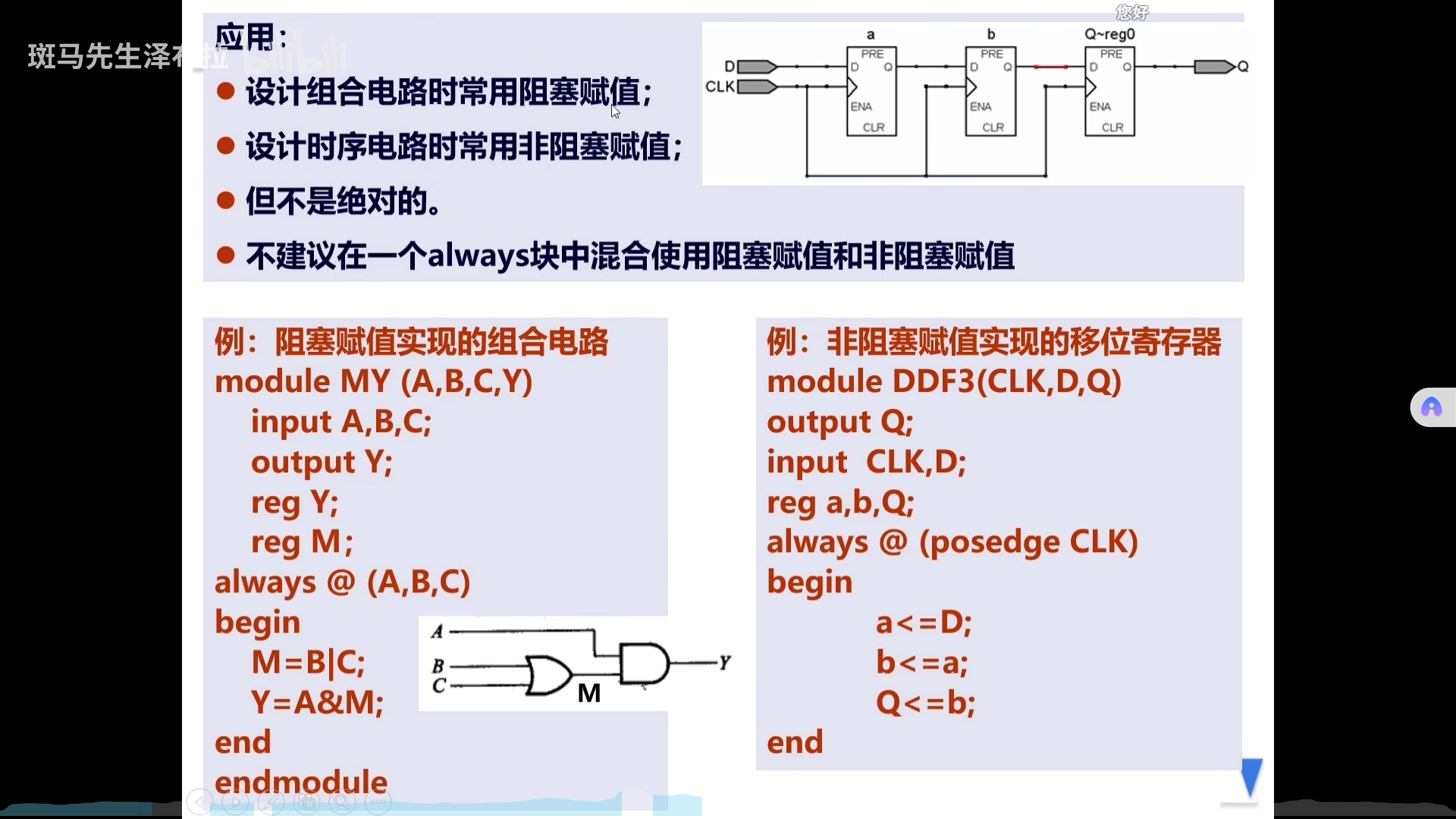

阻塞赋值与非阻塞赋值

时序电路常使用非阻塞<=赋值

举例

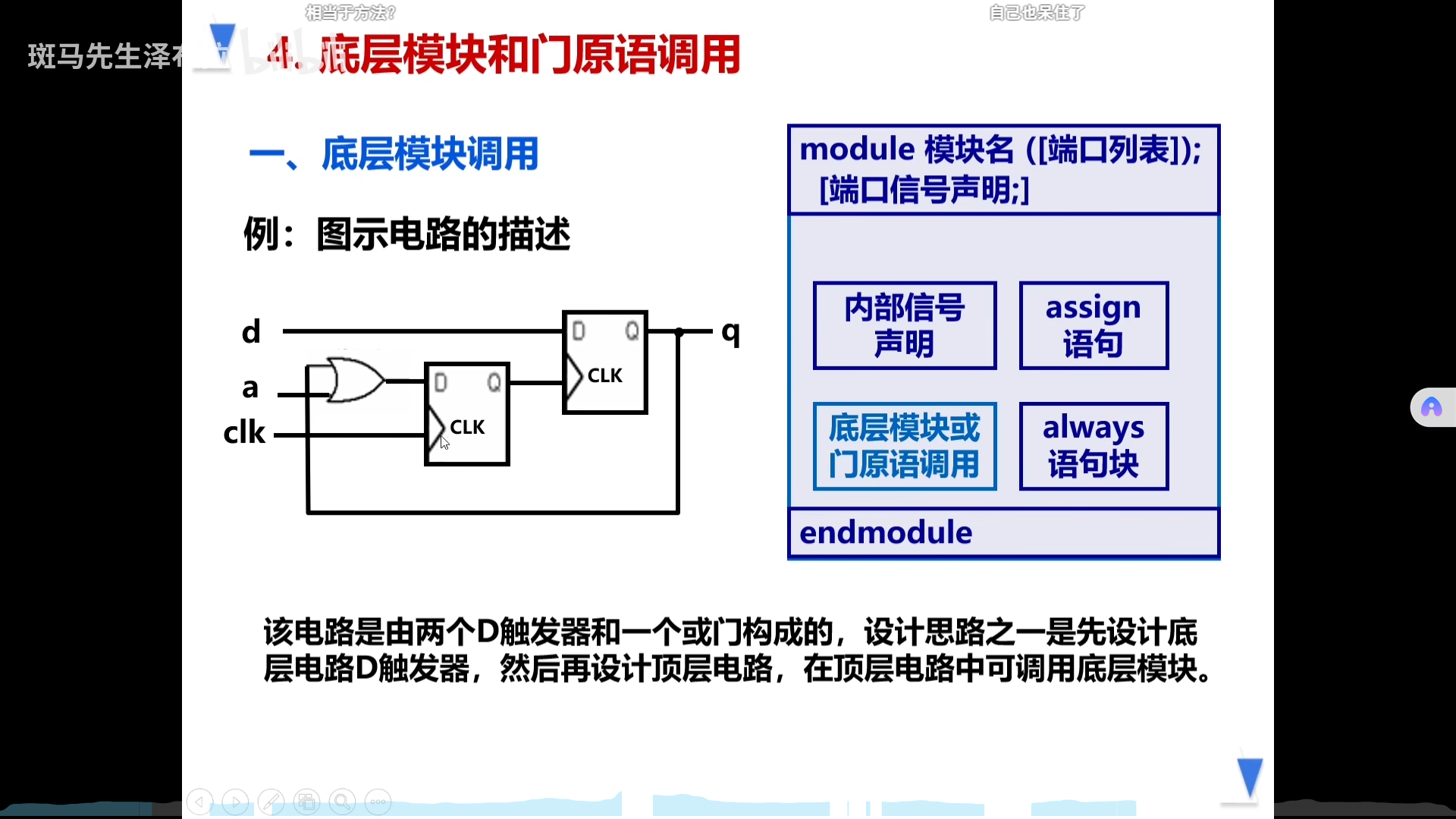

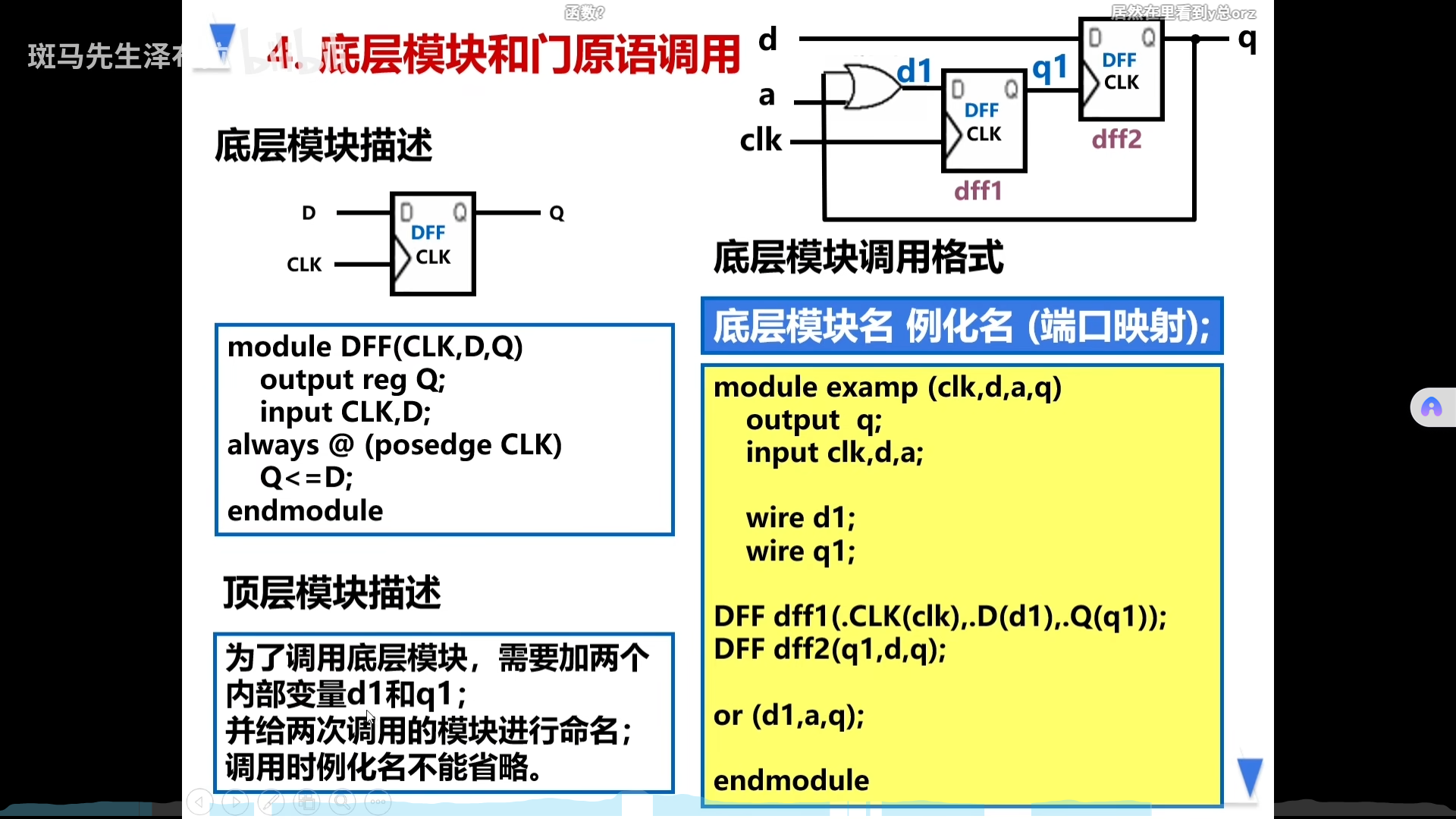

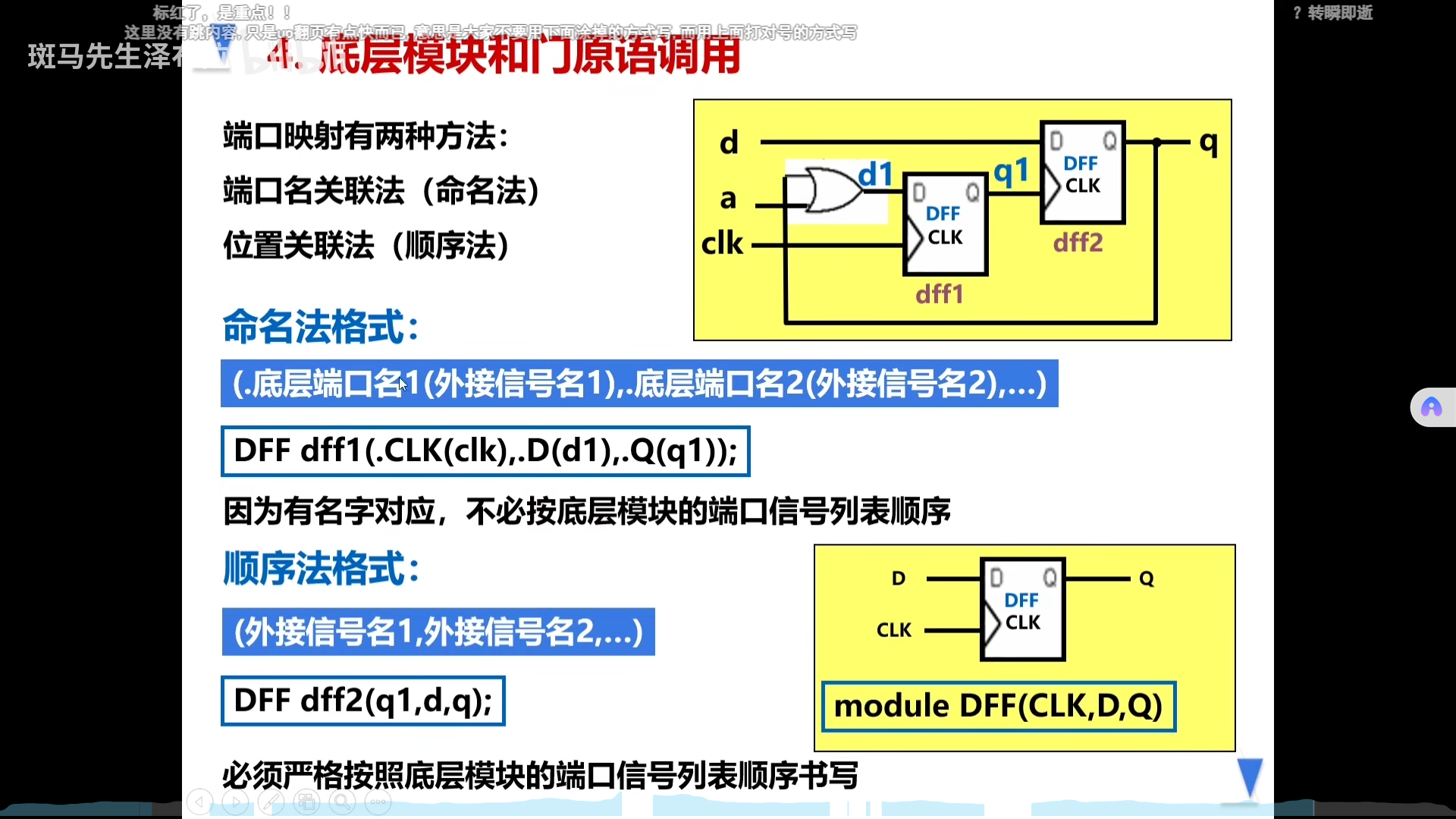

底层模块

例化时采用.x(x)形式进行例化,即命名法格式

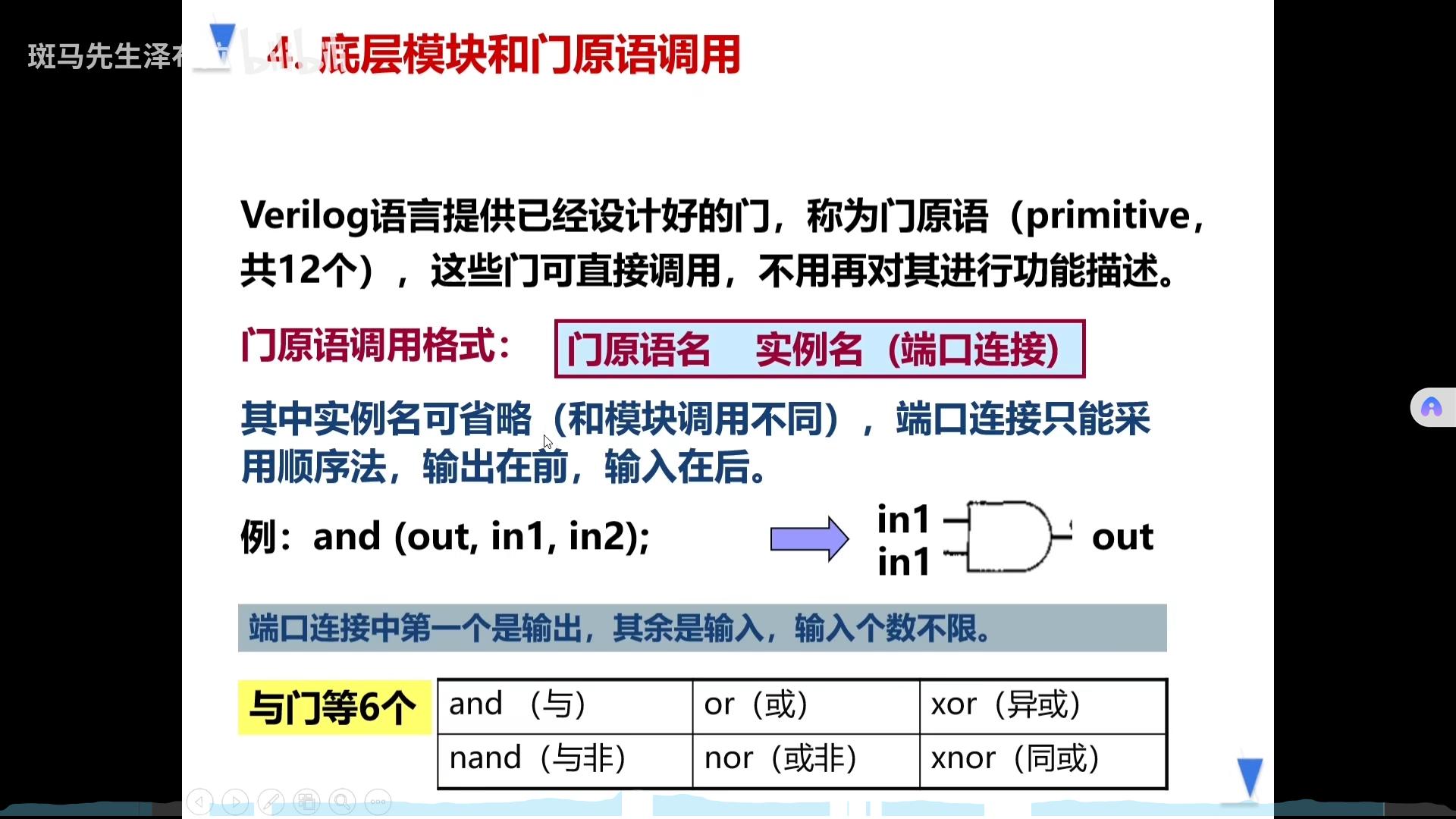

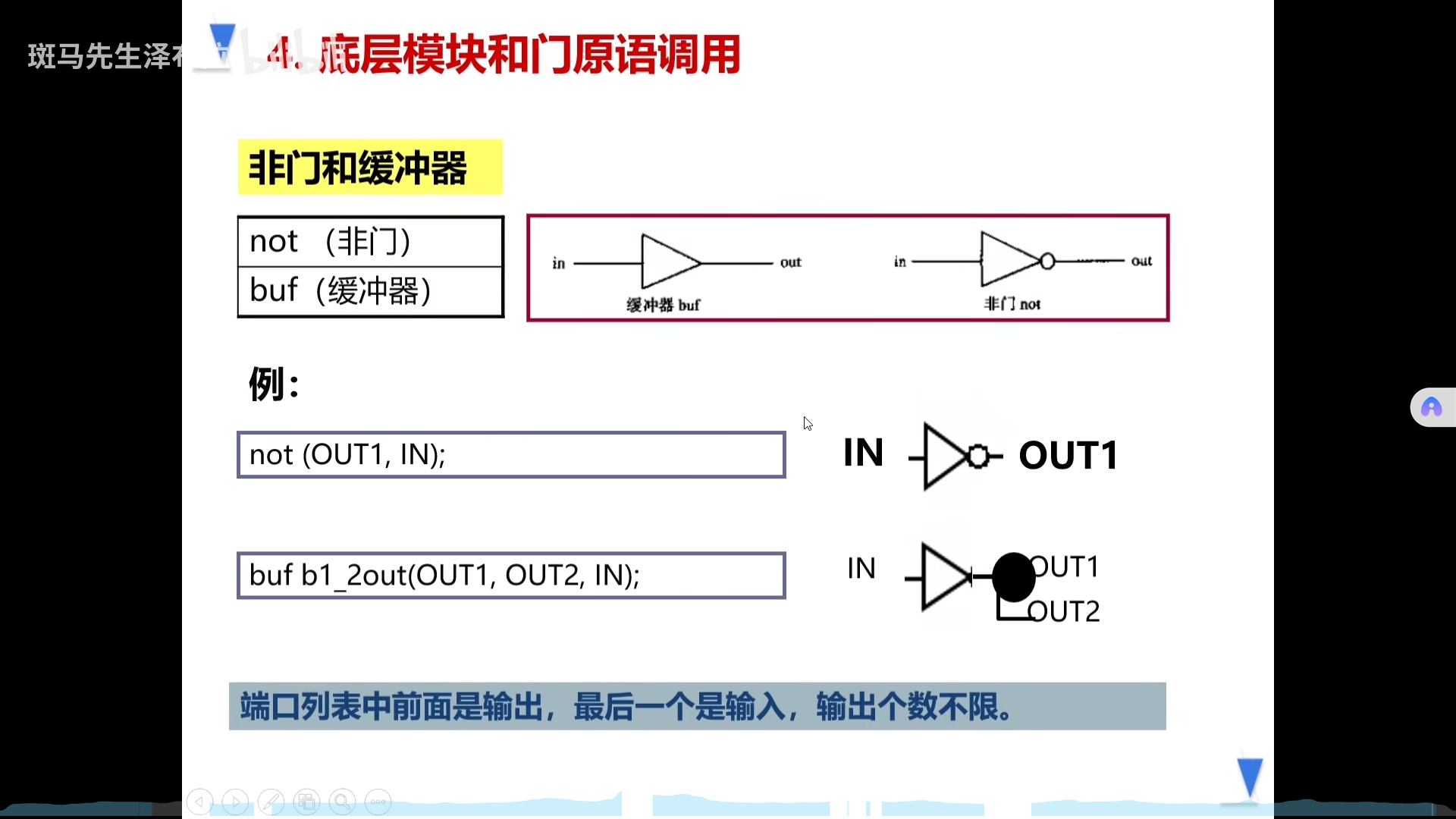

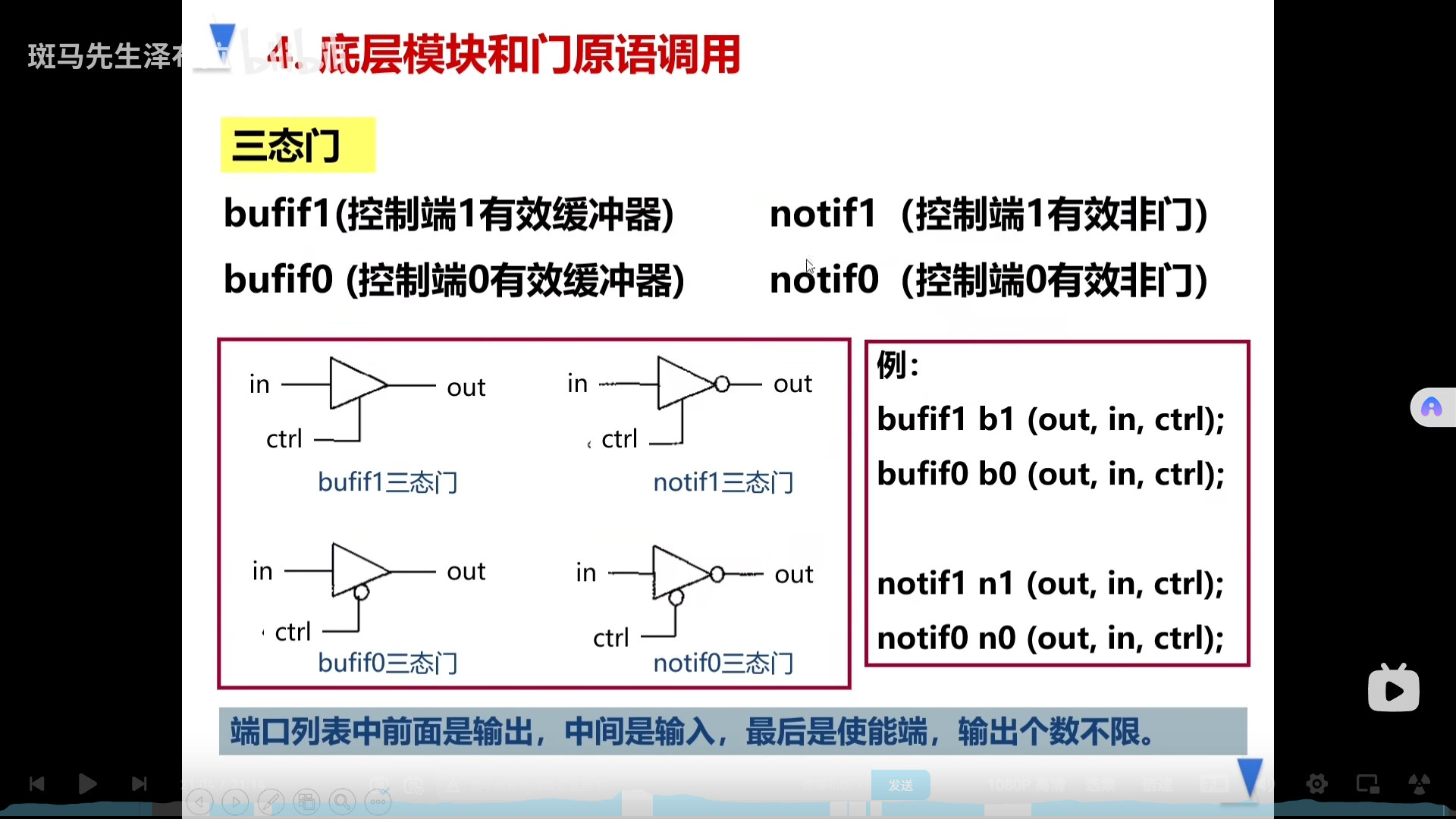

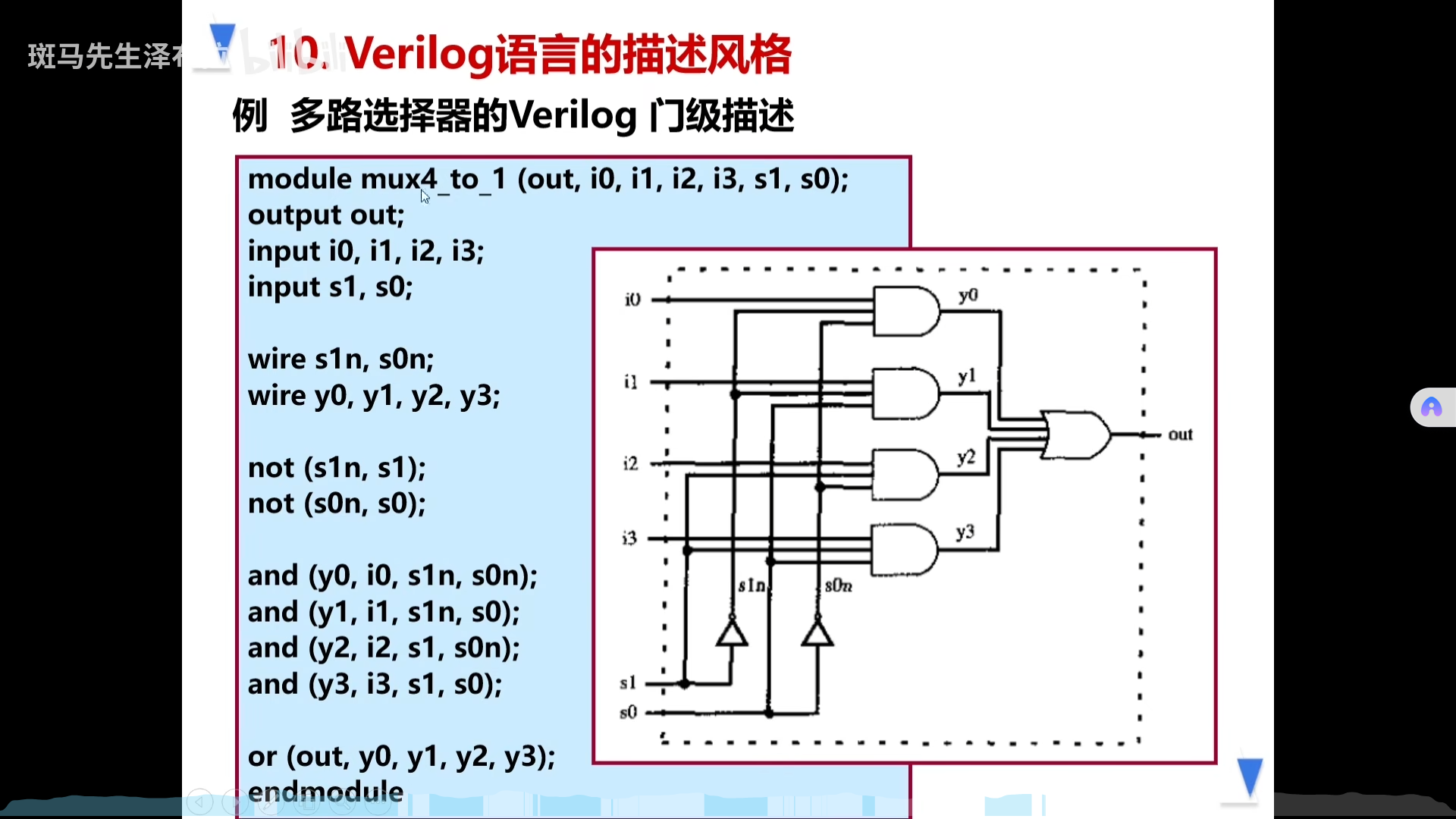

门原语调用

基本用不到

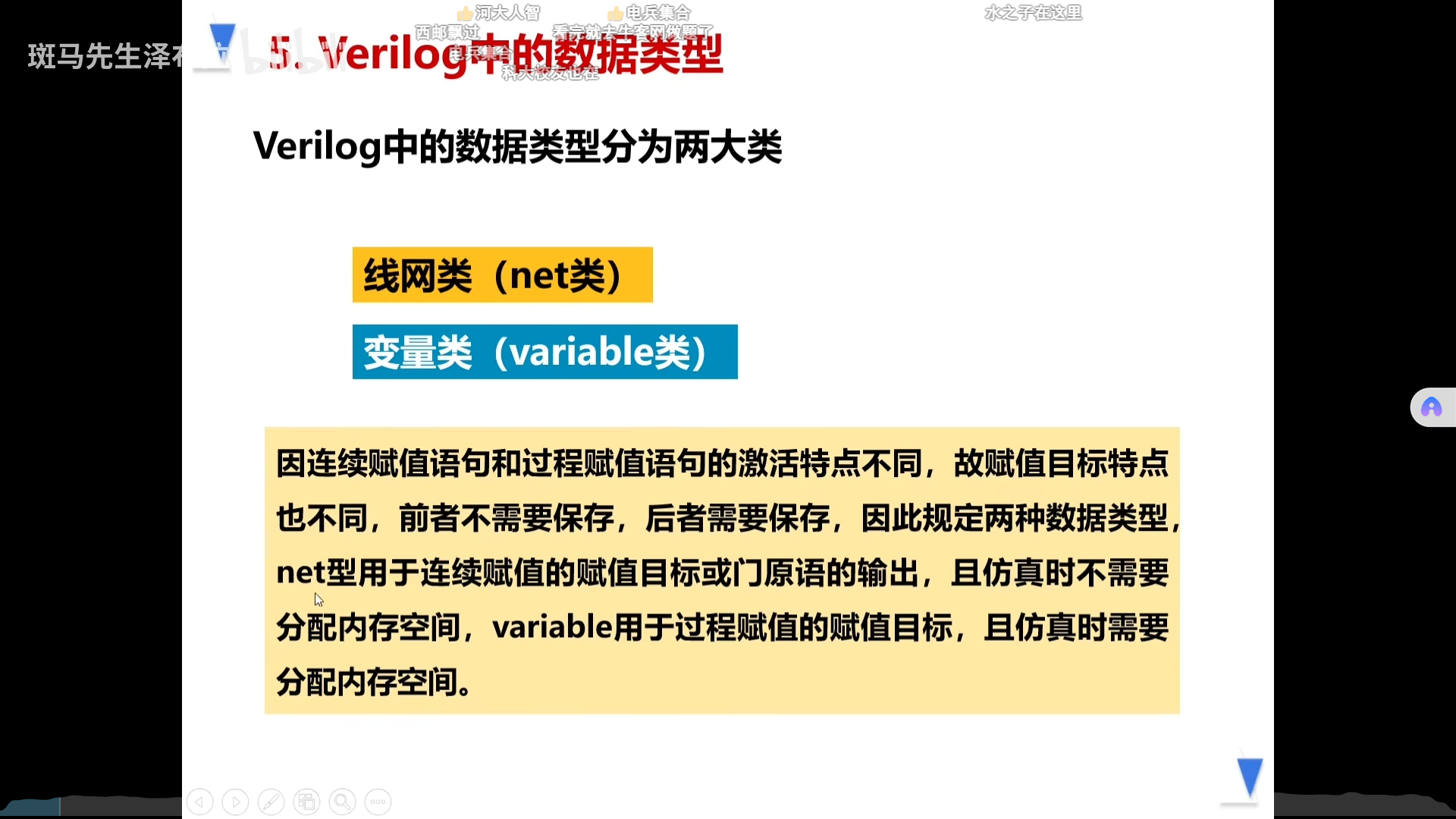

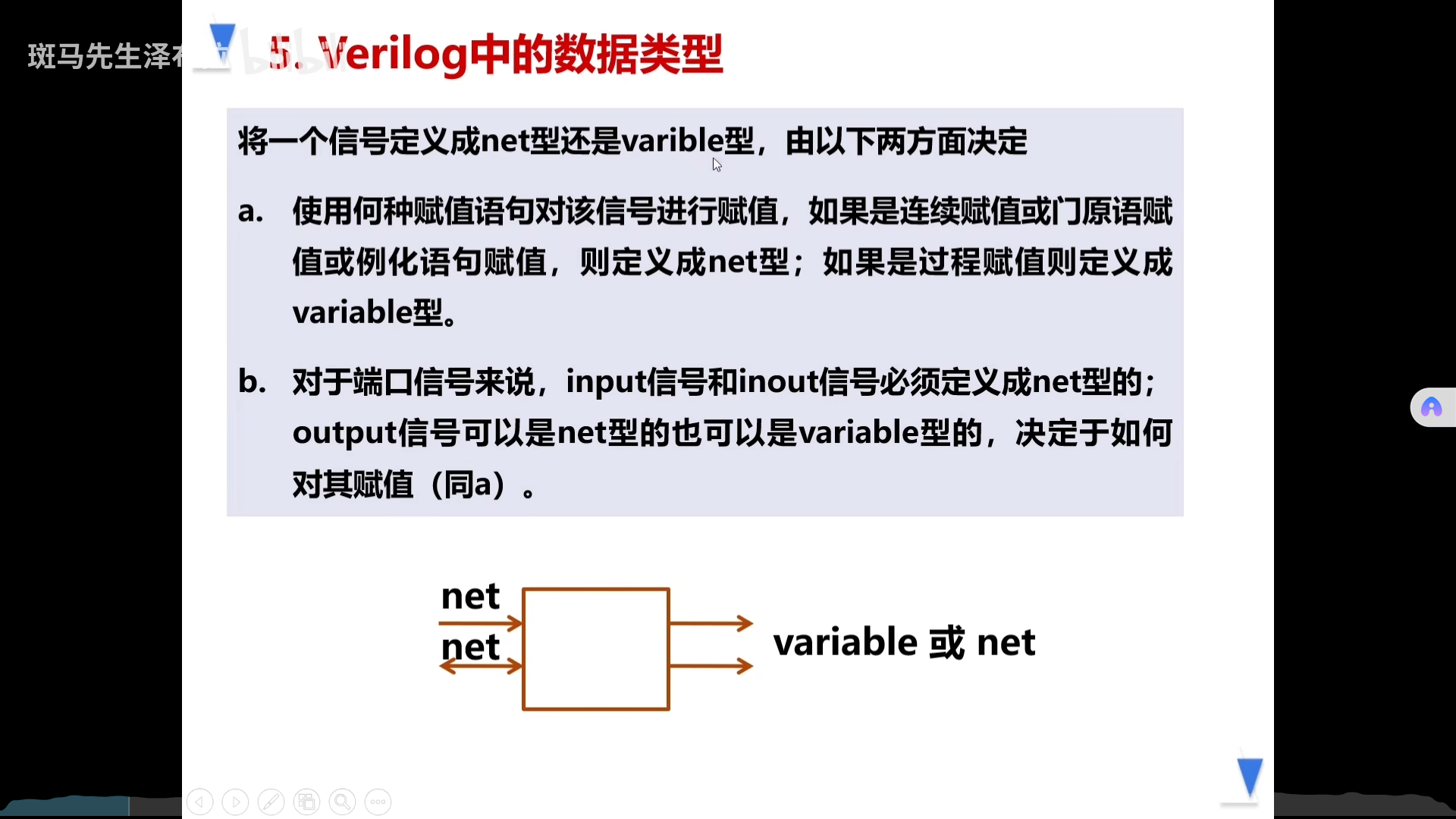

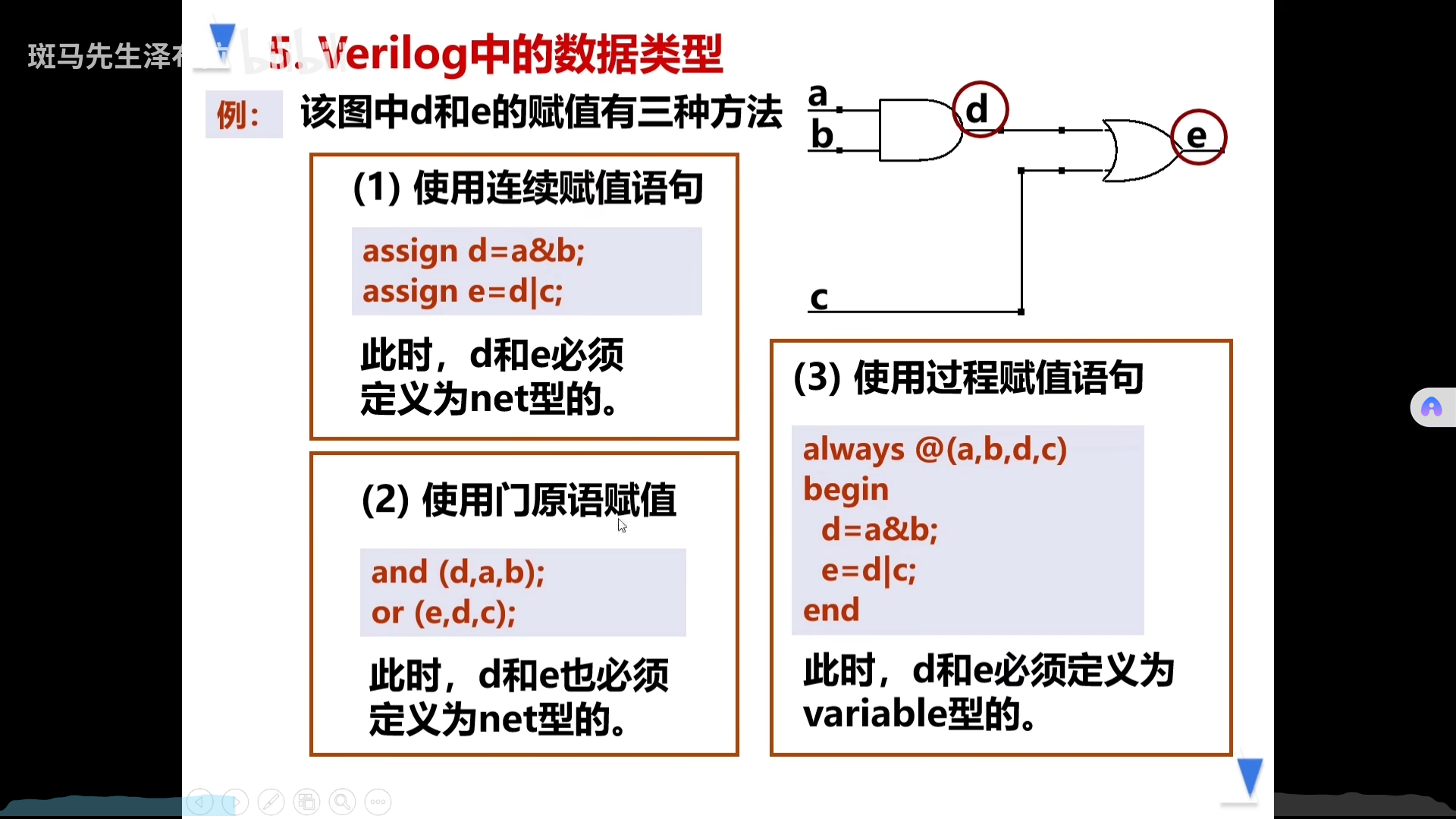

verilog数据类型

wire reg

input,inout信号必须为net形,output随意

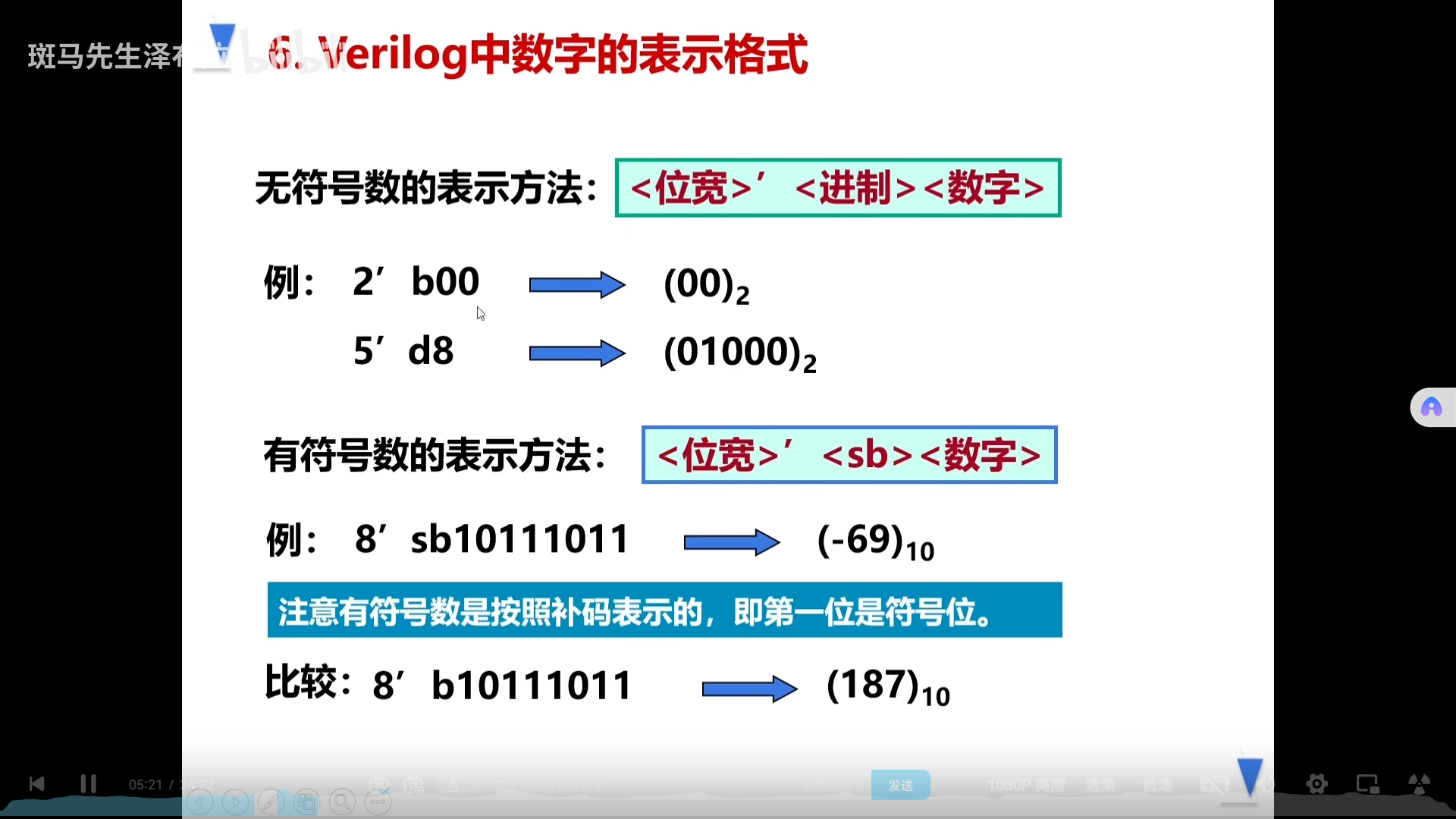

数字表示格式

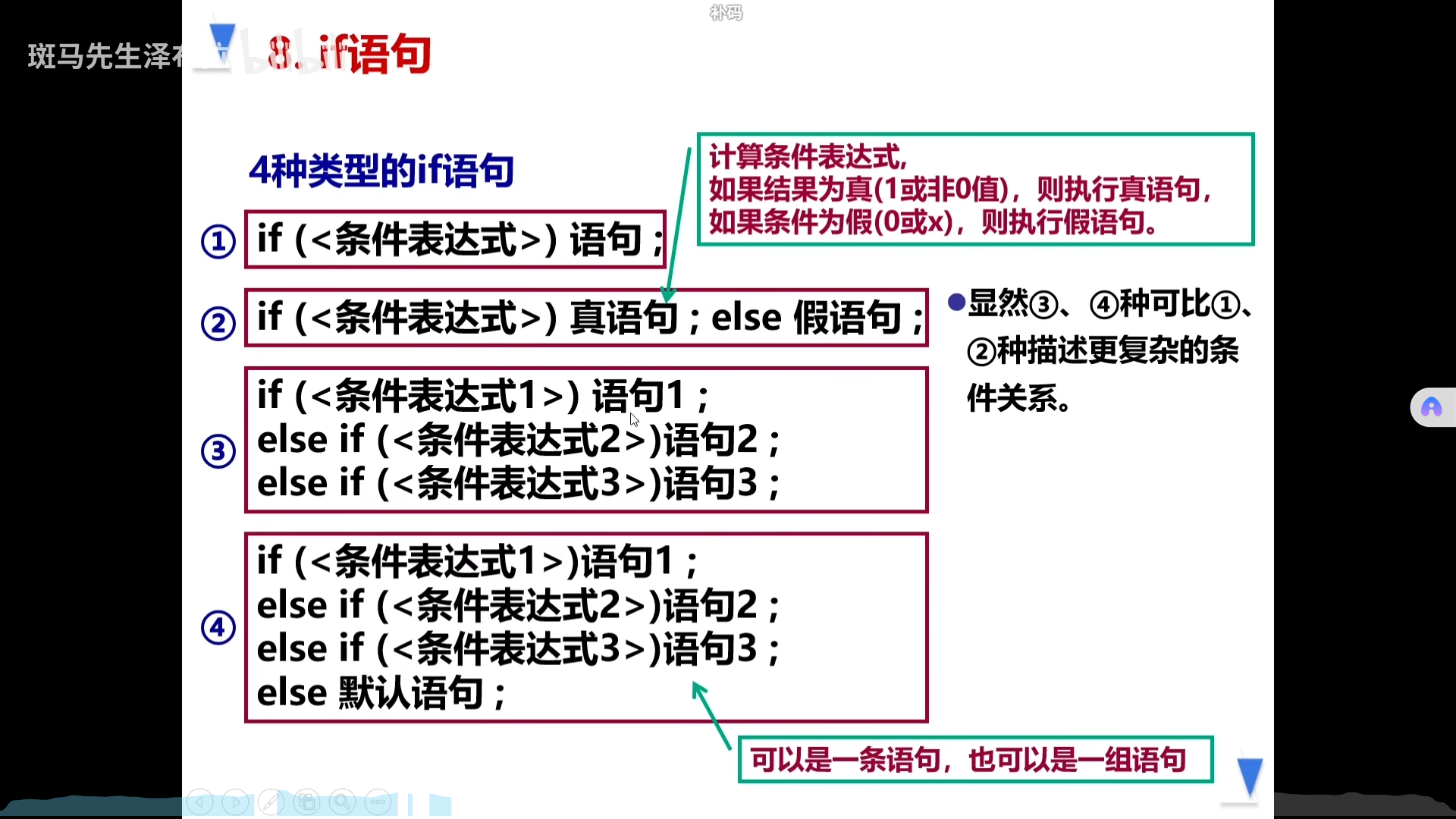

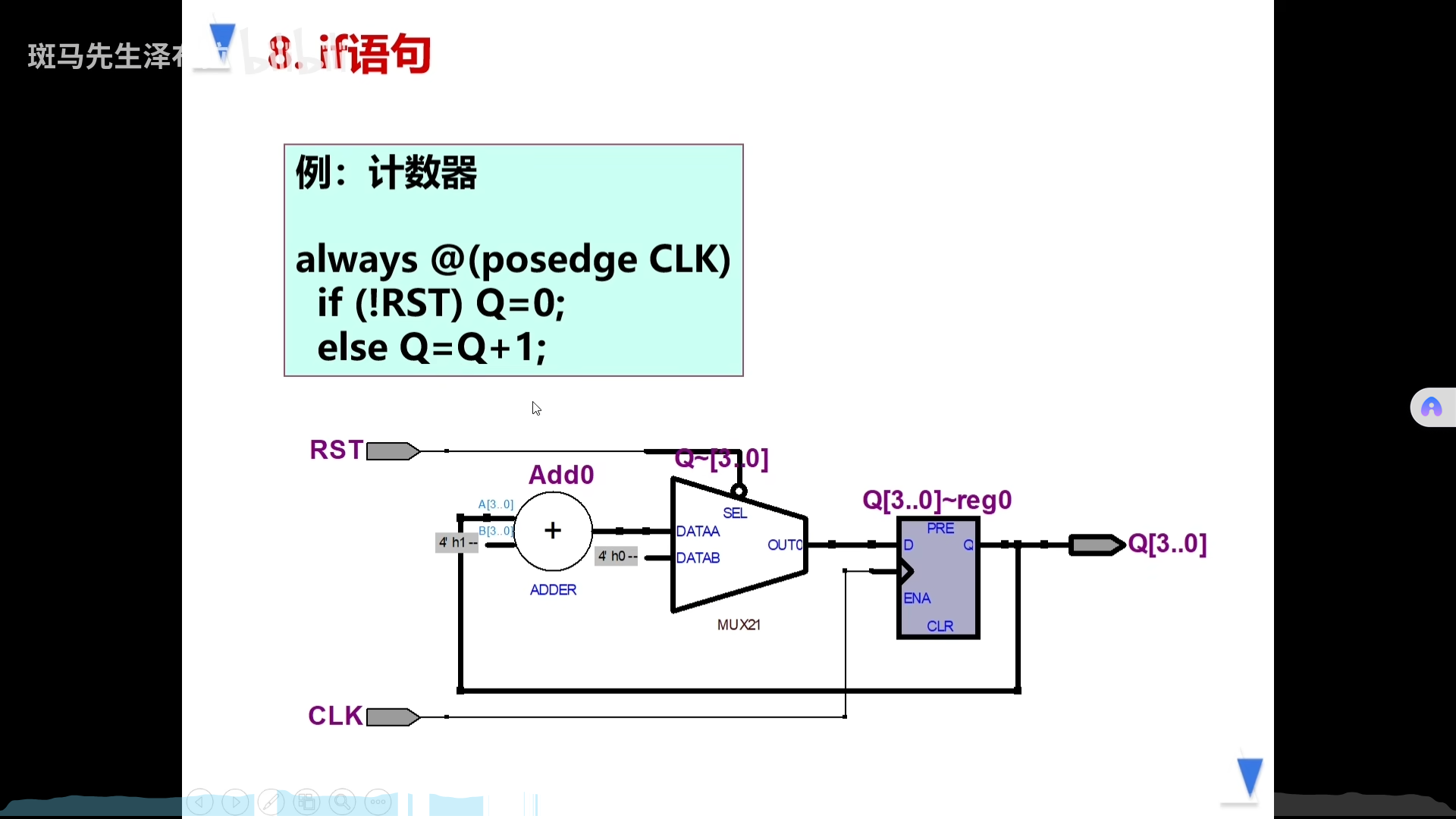

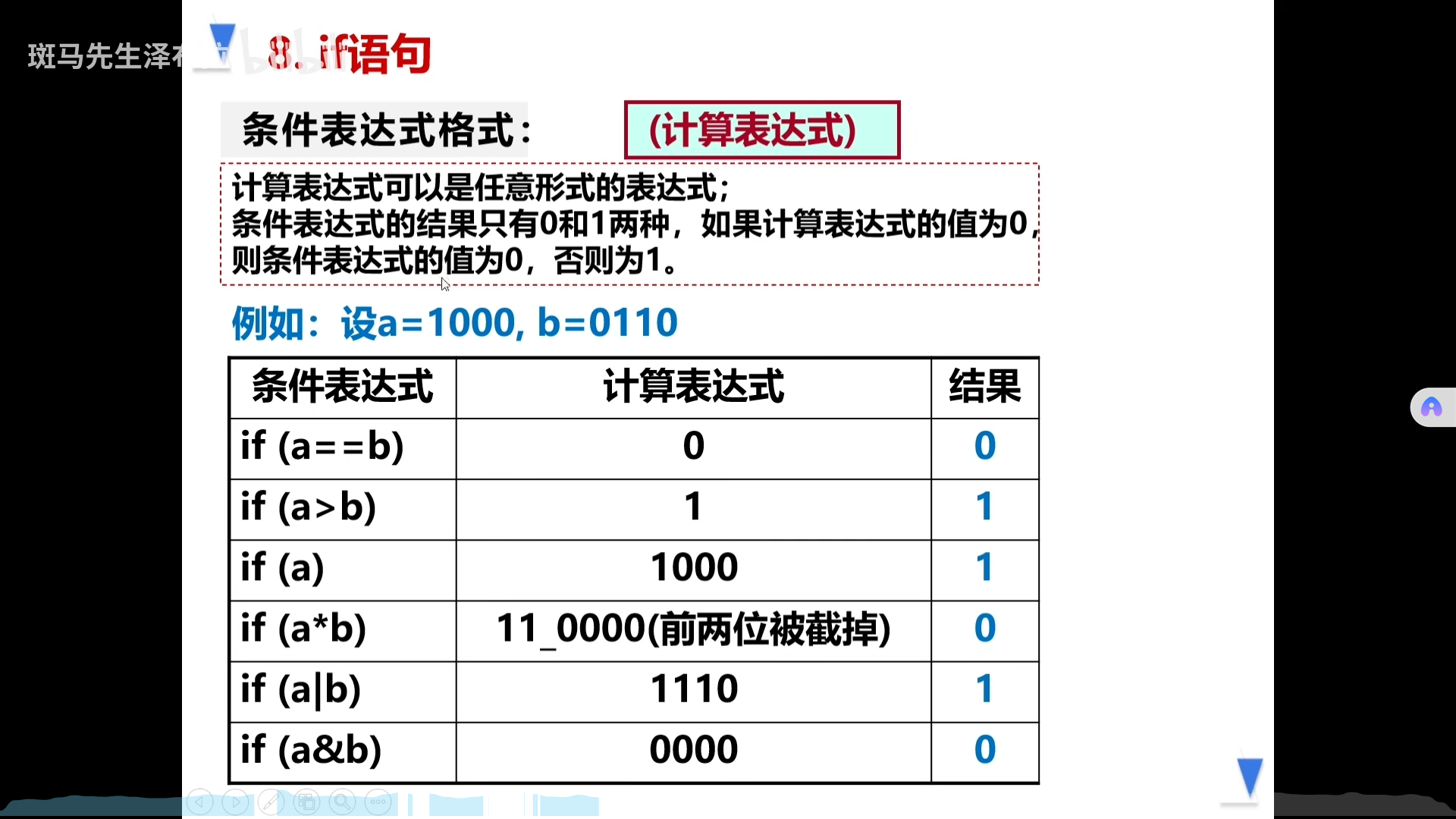

if语句

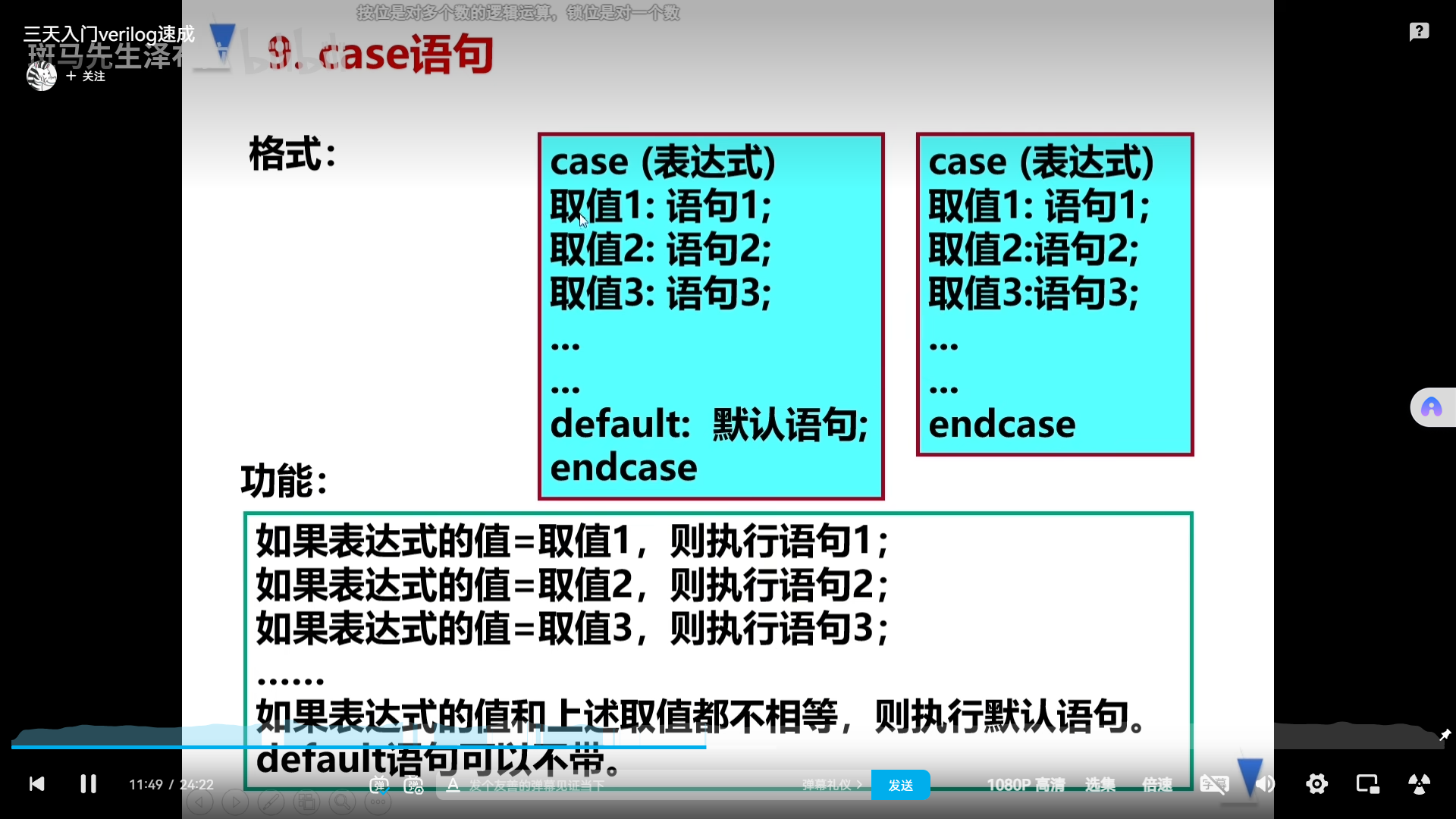

case语句

case endcase

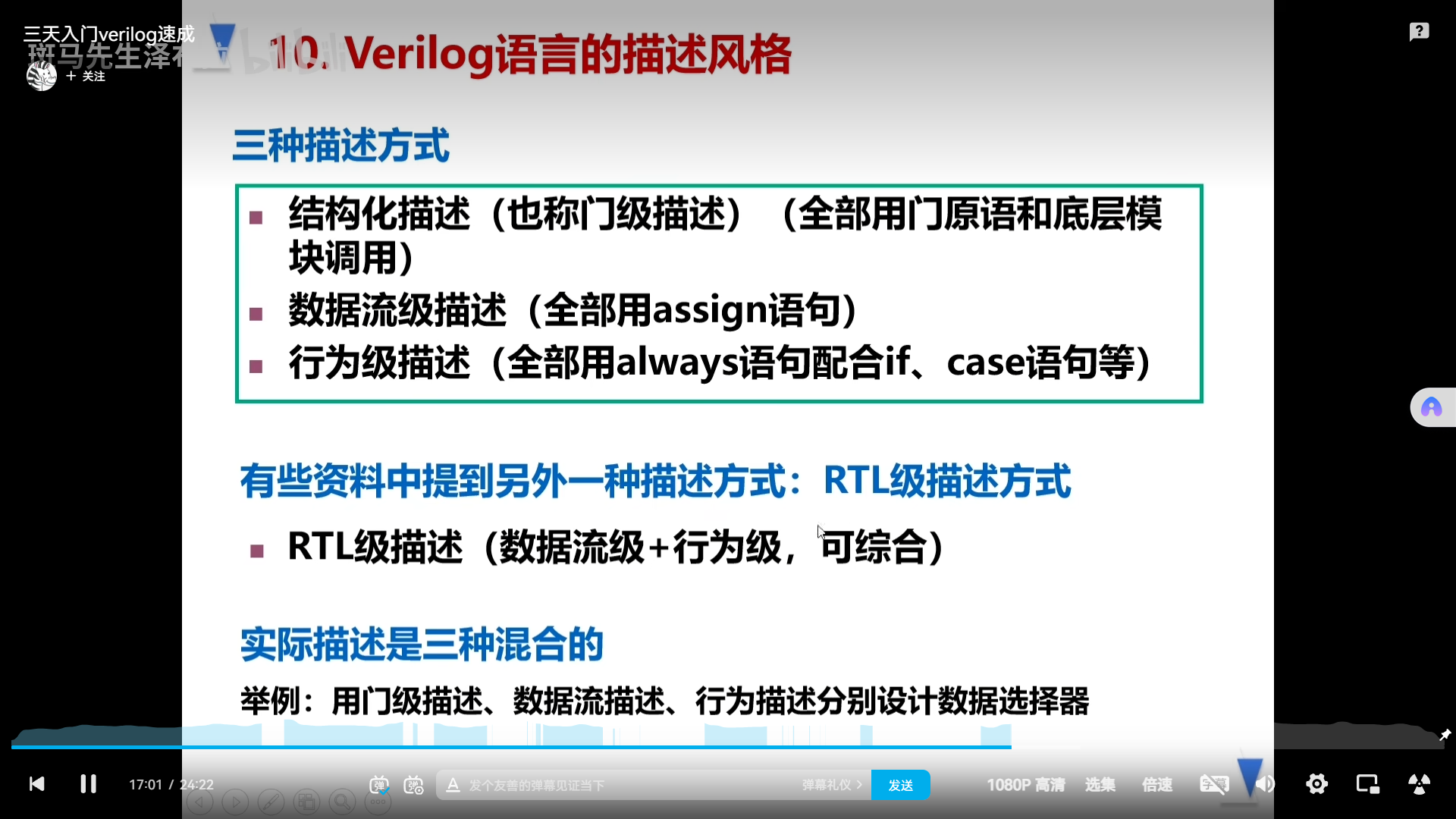

语言描述风格

下面这种用的最多

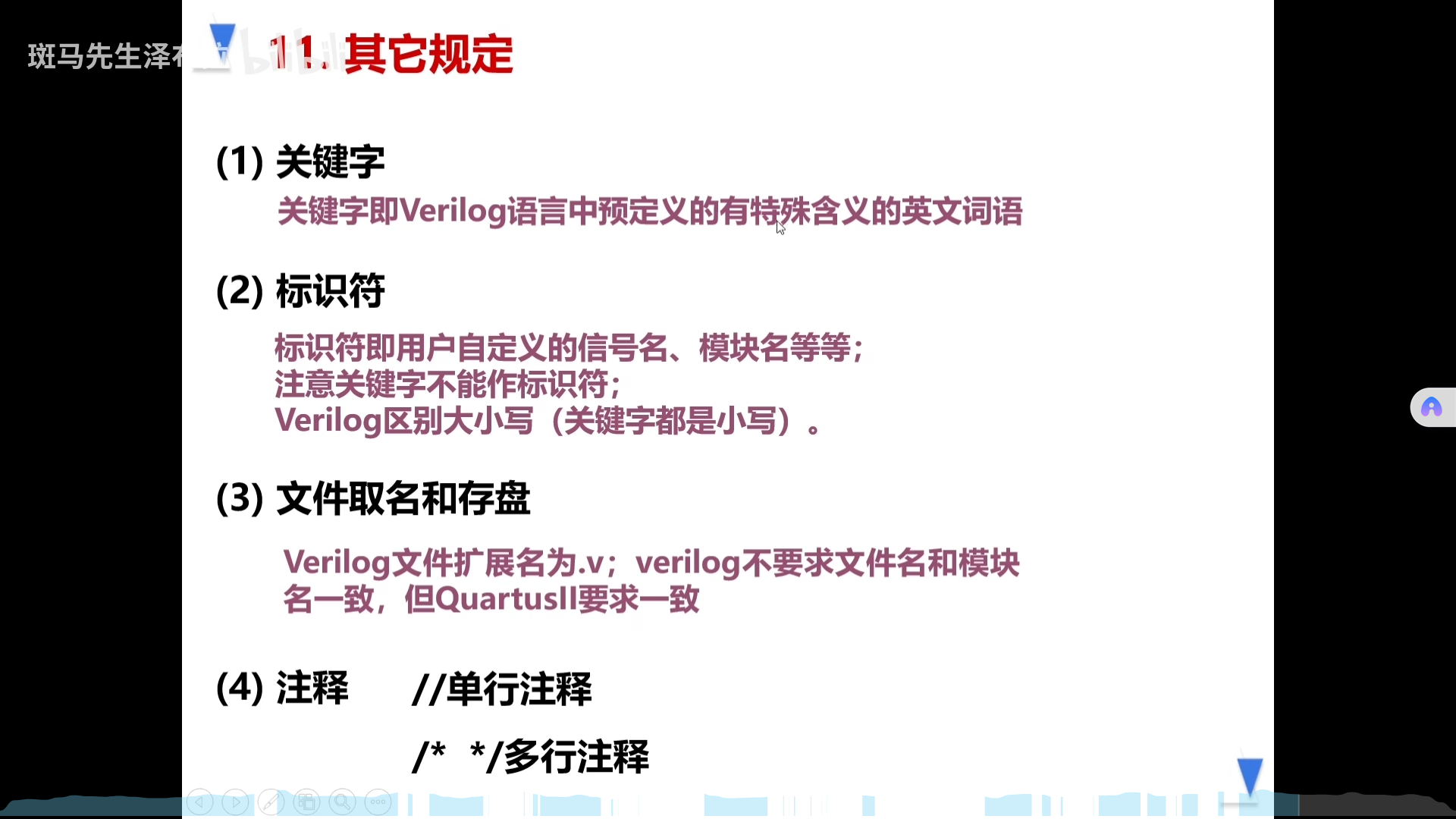

其他规则